Design

*Seminar* '96

**SEMINAR**

**MANUAL**

**TEXAS

INSTRUMENTS**

## **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilised to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

**TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORISED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR OTHER CRITICAL APPLICATIONS.**

Inclusion of TI products in such application is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimise risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimise inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright ©1997, Texas Instruments Incorporated.

# Texas Instruments Data Transmission Seminar '96

## Mixed Signal & Analog Products

**1996**

**DATA TRANSMISSION**

**SEMINAR**

contributions by:

Eilhard Haseloff

Heinz-Peter Beckemeyer

Jean-Claude Baumer

# **CONTENTS**

|                  |                                                               |            |

|------------------|---------------------------------------------------------------|------------|

| <b>CHAPTER 1</b> | <b>INTRODUCTION</b>                                           | <b>1-1</b> |

| <b>CHAPTER 2</b> | <b>BASICS AND PRACTICAL<br/>EXAMPLES OF DATA TRANSMISSION</b> | <b>2-1</b> |

| <b>CHAPTER 3</b> | <b>PROTECTIVE CIRCUITS</b>                                    | <b>3-1</b> |

| <b>CHAPTER 4</b> | <b>TTL-TYPE DATA TRANSMISSION</b>                             | <b>4-1</b> |

|                  | - IEEE 488                                                    | 4-2        |

|                  | - IEEE 1284                                                   | 4-11       |

| <b>CHAPTER 5</b> | <b>UNBALANCED DATA TRANSMISSION</b>                           | <b>5-1</b> |

|                  | - RS-232                                                      | 5-2        |

|                  | - UART                                                        | 5-23       |

|                  | - IrDA                                                        | 5-44       |

|                  | - RS-423                                                      | 5-52       |

|                  | - METER BUS                                                   | 5-56       |

| <b>CHAPTER 6</b> | <b>BALANCED DATA TRANSMISSION</b>                             | <b>6-1</b> |

|                  | - RS-422                                                      | 6-3        |

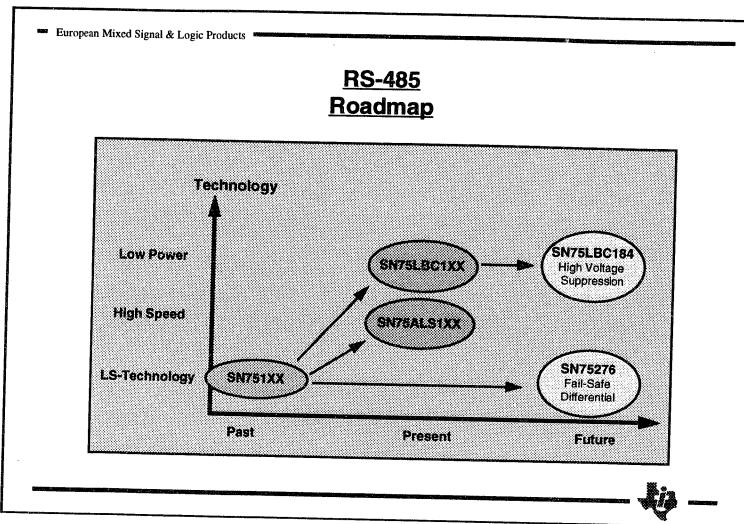

|                  | - RS-485                                                      | 6-3        |

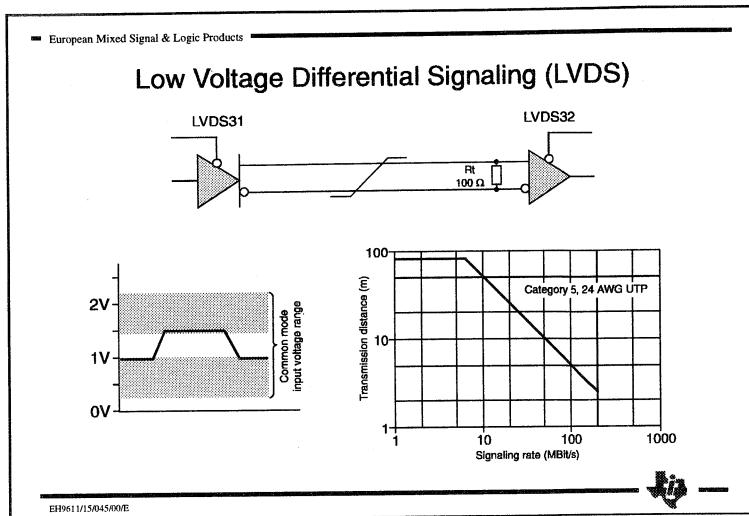

|                  | - LVDS                                                        | 6-44       |

|                  | - CAN                                                         | 6-42       |

| <b>CHAPTER 7</b> | <b>ADVANCED HIGH-SPEED INTERFACES</b>                         | <b>7-1</b> |

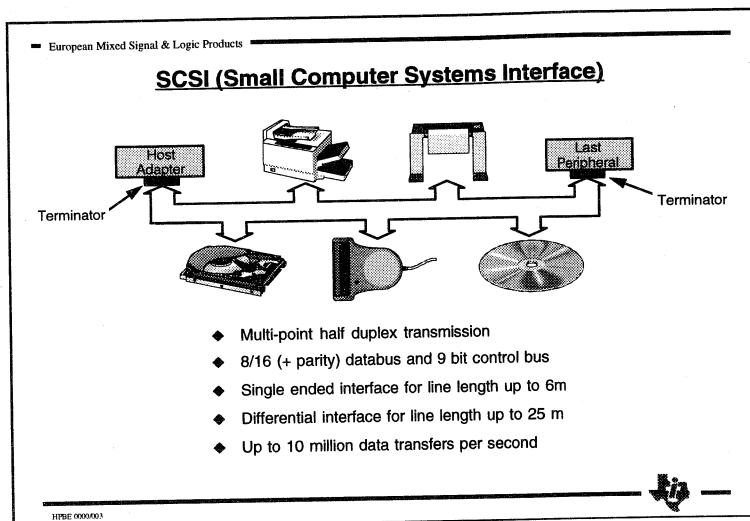

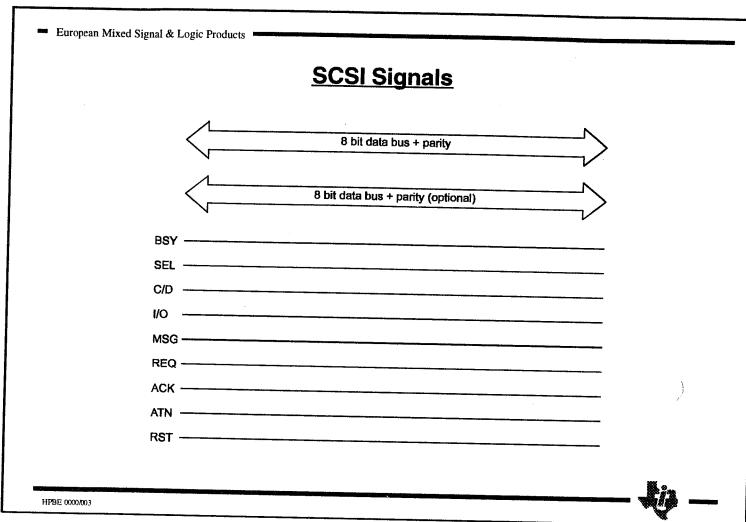

|                  | - SCSI                                                        | 7-2        |

|                  | - IEEE 1394                                                   | 7-29       |

— European Mixed Signal & Logic Products —

# Introduction

JCB SEMINAR DATA TRANS INTRO PPT

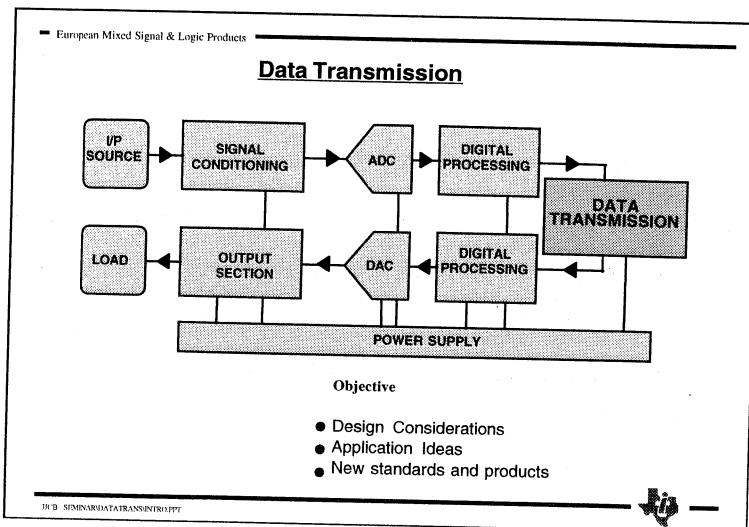

## Data Transmission

Data Transmission as part of Texas Instruments' Linear Products portfolio is concerned with the standards involving transmitting data at relatively high speeds down long line lengths, the considerations for which are primarily of an analog more than a digital nature. Likewise the design of data transmission ICs requires experienced analog engineers to implement functions such as slew rate limiting, receiver filtering and common-mode protection.

In this year's seminar we will review single ended transmission standards and differential transmission standards and high speed data transmission protocols. We will explore the circumstances under which to select a given standard and review design considerations when implementing the standard.

### The Need for Transmission Standards

Data transmission standards evolved for two main reasons: From the need to transmit data reliably over long distances, and to provide a standard interface to facilitate communication between equipment from different suppliers. Although TTL/Logic signal levels and products can be used, they generally lack the power handling capabilities, robustness and noise margins required for reliable transmission. Indeed for backplane equipment, TTL is no longer specified for the newer high speed standards, such as Futurebus+ which uses BTL transceivers. In general the standards concerned with transmitting data over long distances incorporate wider voltage swings, increased robustness and higher power outputs than can be delivered using conventional 'Logic' products. Similarly the sub-micron technologies used in the fabrication of today's logic devices cannot provide the power handling and robustness necessary for successful long distance transmission.

### **Specialised Technologies**

This leads to the need for specialist ICs, and technologies, to meet the exacting requirements of these transmission standards. The traditional technological answer has been to utilise the inherent robustness afforded by bipolar technologies, however the additional need for low power consumption and high levels of integration no longer makes this attractive. SC manufacturers are now having to develop their technologies to accommodate these requirements. TI has introduced its proprietary LinBiCMOS\* technology combining the robustness of bipolar together with the power consumption and integration afforded by CMOS. Other manufacturers are using pure CMOS and integrating Schottky diodes to the same end. The result is very specialised and reliable products that are able to withstand the harsh environment unique to data transmission products.

Texas Instruments has been a leading supplier of data transmission products for many years, and is continually innovating new fields. Although the following sections are limited to the more common interface standards, TI is actively involved in many new emerging standards and markets, the high speed serial data link evolving from the IEEE1394 committee and multiplex wiring systems such as ABUS, CAN and VAN. The reader is advised to contact a TI representative for information on these product areas.

With the considerable expertise in design, product definition and range of technologies Texas Instruments is the ideal choice for supplying your data transmission product requirements.

### Types of Transmission

Most commonly transmission of data occurs directly from one logic gate to another. Low power Schottky TTL and HCMOS can operate at clock frequencies of up to 40MHz. Interconnects must be short (a few 100s of millimetres) and special care taken to assure adequate noise margin and minimum line reflections. The higher speeds of Advanced Schottky TTL and ECL gates place even more emphasis on properly terminated, well defined lines.

There are limiting factors to directly driving over longer distances using standard logic devices. The most important of these is the environmental noise level, whether this is directly radiated or by ground shift potentials. The guaranteed noise margin of standard TTL is +/- 0.4V and is insufficient in most applications.

Many specialised data transmission devices have been developed to overcome this problem, they work by increasing the signal level on a line and thereby improving the noise margin. The techniques involved use single ended or differential (balanced) operation with either voltage mode or current mode drive to the line.

Twisted pair and coax lines are used for single ended drive over longer distances but single and multi wire can be used where the data rate is low and line lengths are short. For differential data transmission a twisted pair is normally used.

### **Single-Ended Transmission**

Numerous integrated circuit devices are available for driving single ended data transmission lines. Some are general purpose and others have been designed to meet specific industrial standards.

Advantages and disadvantages of single ended drivers :

#### Advantages

Simplicity : minimum connections

Low cost

#### Disadvantages

Radiates RFI easily

Poor noise immunity

Coax improves noise but is expensive

Limited line lengths and data rates due to susceptibility to interference signals

### **Differential (balanced) Transmission**

The ability to transmit data from one location to another without errors requires immunity to noise. At high data rates, on long lines or under noisy conditions, differential data transmission has an advantage because it is more immune to noise interference than single-ended transmission.

Voltages induced onto the data lines by ground noise or switching transients appear as common-mode signals at the receiver input. Since the receiver has a differential input it corresponds only to the differential data signal. Differential drivers and receivers can operate safely within specified common-mode voltage ranges. Differential line drivers and receivers are designed for general purpose applications as well as specific standards.

Advantages and disadvantages of differential (balanced) data transmission relative to single ended transmission are :

#### Advantages

High common mode noise voltage rejection

Reduced line radiation - less RFI

Improved speed capabilities

Drive longer line lengths

#### Disadvantages

Slightly higher costs (sometimes)

Must be used with twisted pair or other types of balanced transmission lines

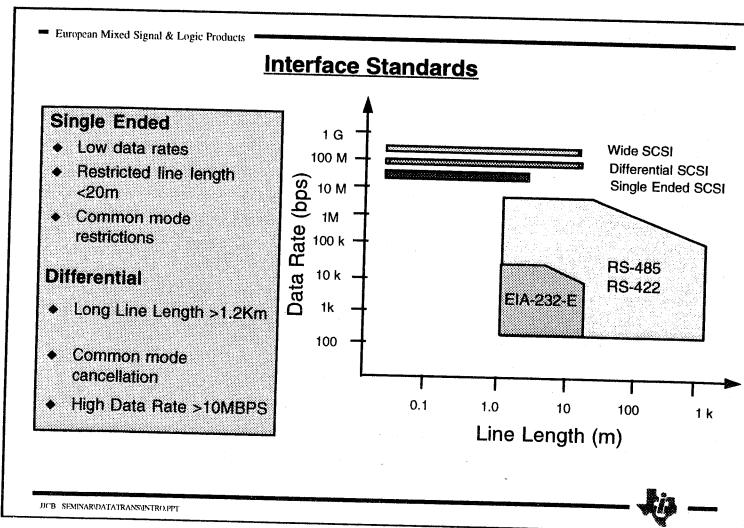

Referring to Figure 'Interface Standards' we can see the relationship of each transmission standard when comparing data rate and line length.

— European Mixed Signal &amp; Logic Products —

### Known Interface Standards

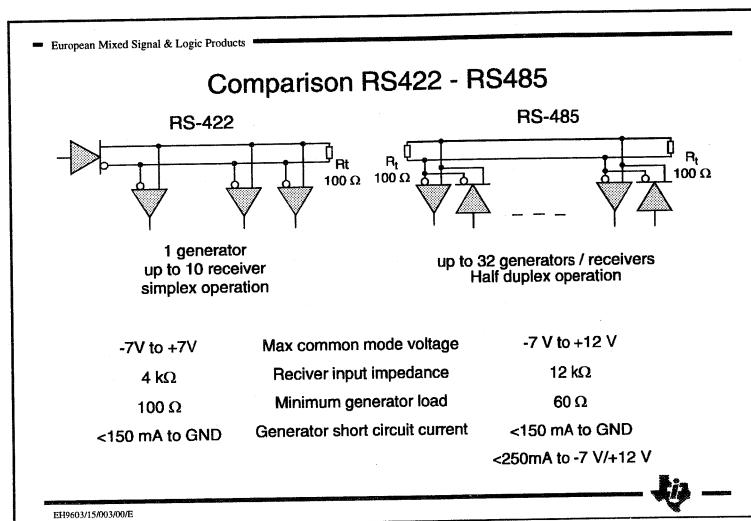

| Parameter                                      | EIA-232                      | RS-423-A                 | RS-422-A                        | RS-485                     |

|------------------------------------------------|------------------------------|--------------------------|---------------------------------|----------------------------|

| Mode of Operation                              | Single-Ended                 | Single-Ended             | Differential                    | Differential               |

| Number of Drivers and Receivers                | 1 Driver<br>1 Receiver       | 1 Driver<br>10 Receivers | 1 Driver<br>10 Receivers        | 32 Drivers<br>32 Receivers |

| Maximum Cable Length (m)                       | 15                           | 1200                     | 1200                            | 1200                       |

| Maximum Data Rate (bps)                        | 20 k                         | 100 k                    | 10 M                            | 10 M                       |

| Maximum Common-Mode Voltage (V)                | +25                          | +6                       | 6 to -0.25                      | 12 to -7                   |

| Driver Output Unloaded Levels (V)              | +5                           | +3.6                     | +2                              | +1.5                       |

| Driver Load ( $\Omega$ )                       | +15                          | +6                       | +5                              | +5                         |

| Driver Slew Rate                               | 3 k to 7 k<br>30 V/μs (Max.) | 450 (Min)                | 100 (Min)                       | 60 (Min)                   |

| Driver Output Short Circuit Current Limit (mA) | 500 to V <sub>CC</sub>       | 150 to GND               | 150 to GND<br>250 to - or +12 V | 12 k                       |

| Driver Output Resistance                       | Power on                     | NA                       | NA                              | NA                         |

| High Z state ( $\Omega$ )                      | Power off                    | 300                      | 60 k                            | 60 k                       |

| Receiver Input Resistance ( $\Omega$ )         | 3 to 7                       | 4                        | 4                               | 12                         |

| Receiver Sensitivity                           | +3 V                         | +200 mV                  | +200 mV                         | +200 mV                    |

JCB SEMINARDATA/TRANSINTRO.PPT

### **Single Ended Transmission : EIA/TIA-232**

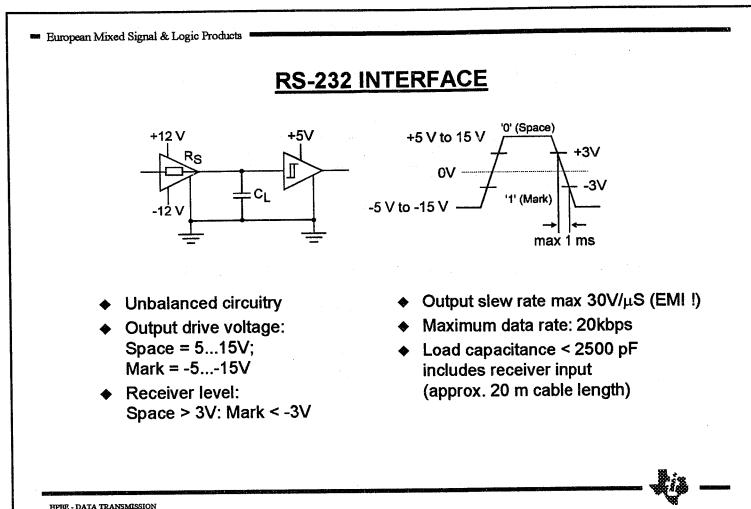

EIA-232 or 'Recommended Standard' 232 is defined in the ANSI (American National Standard Institution) specification as "The Interface Between Data Terminal Equipment and Data Circuit-Terminating Equipment Employing Serial Binary Data Interchange". The standard employs a single ended serial transmission scheme and outlines the set of rules for exchanging data between computer equipment, originally this being a Computer Terminal (DTE) and a modem (DCE). The standard has evolved over the years with the latest 'E' revision released in July 1991. The standard is now known as EIA/TIA-232-E, with EIA standing for the Electronic Industries Association and TIA for the Telecommunications Industry Association.

As with previous revisions of the standard the maximum data rate is defined as 20 k bits per second (kbps) although there are now a number of software applications that now push this data rate above 200 kbps, well outside the standard. The 'C' revision defined the maximum line length as 15 metres however this failed to comprehend the type of cable used and consequently the load capacitance on the line driver. Both the 'D' and 'E' revisions addressed this by more correctly defining the line length in terms of load capacitance. The maximum load capacitance is specified as 2500 pF that translates using standard cables to between 15 and 20 metres. Line length and data rate are limited as the standard employs single ended communication which is prone to external factors. For longer line lengths and higher data rates a differential balanced line communication link is essential.

### **Differential Transmission : RS422-A**

The balanced transmission line standard EIA RS-422 was developed in 1975 to interface a host computer's data, timing or control lines to its peripherals. The standard was revised (RS-422A) in December 1978 bringing it in line with its present specification.

A RS-422 line allows for only one way communication (simplex) mode. By using a differential twisted pair transmission media (not specified in the standard) and a RS-422 receiver with its minimum 7V common mode voltage capacity it is less susceptible to noise picked up in hostile environments via the long cables allowed by the standard. Each driver can drive up to 10 receivers. The specification in the standard places no restrictions on minimum or maximum operating data rates but rather on the relationship of transition speed to a unit interval. However, data rates up to 10Mbps are supported and a line length up to 1200 metres is given as a guide-line , but not at the maximum data rate.

When operating at low data rates (below 200kps) or at any speed where the ratio of the driver's output rise time to the one way propagation delay time of the cable exceeds ten, the cable will not act as a true transmission line and therefore termination is not absolutely necessary. Under all other conditions, the cable loading can no longer be considered as a lumped parameter but must be considered as a transmission line.

The characteristic impedance of twisted pair cable is a function of frequency and cable type, however typical twisted pair cable impedance's lie in the range 100\* to 120\*.A termination resistor with an impedance similar to the cable's characteristics impedance should only be connected at the furthest end of the cable.

### **Differential Transmission : RS-485**

RS-485 was primarily an upgrade to the EIA RS-422-A standard utilising the same signal levels but facilitating half duplex multi-point communication. The standard is less complex than the EIA-232 standard as it only specifies the physical layer of the transmission scheme. Hardware such as the connector is left to the user to define. The standard specifies a balanced transmission line whose maximum line length is undefined but is nominally 1.2 km for 24 AWG cable based on 6 dB signal attenuation. The maximum data rate is also undefined but is specified by the relationship of signal rise time to bit time which is influenced both by the line driver and the line length and the line loading. In the majority of applications it is the line length that is the limiting factor on data rate due to signal dispersion. This is discussed in later sections.

### **Single and Differential Transmission : Small Computer Systems Interface (SCSI)**

SCSI is an industry-standard interface, defined by the ANSI, for the interchange of data between computer and computer peripherals. Standard SCSI is a byte wide parallel interface for high speed data transfer over relatively short distances. The SCSI bus is bi-directional and is terminated at both ends of the cable to reduce reflections. For the single ended interface the standard specifies a maximum line length of 6 metres. The maximum data rate is not specified but at present 5 Million Transfers per second (MTps) is achievable using active termination. This can be increased up to 10 MTps using innovative termination as we will discuss later. For longer line length applications, up to 25 metres, the SCSI standard defines the interface using the RS-485 standard as the physical layer. This pushes the data rate to 10 MTps over the full 25 metres which equates to 80 Mbps. A further development of SCSI is 'Wide' SCSI which increases the data bus to 16 bits wide. Using the 10 MTps differential interface this increases the bit rate to 160 Mbps.

■ European Mixed-Signal & Logic Products

**Texas Instruments**

**Data Transmission Product Ordering Information**

|                         |                                                                                                                   |    |     |     |    |   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|----|-----|-----|----|---|

| Prefix                  | SN                                                                                                                | 75 | LBC | XXX | DW | R |

| Temperature Range       | 75 - Commercial (0° to 70°C)<br>65 - Industrial or extended (-40° to 85°C)<br>55 - Military (-55° to 125°C)       |    |     |     |    |   |

| Process Technology      | LVDS - Low Voltage Differential Signaling<br>LSS - Low-Swing MOS<br>ALS - Advanced Low-Power Schottky<br>C - CMOS |    |     |     |    |   |

| Device Number           |                                                                                                                   |    |     |     |    |   |

| Package                 | D / DW - SOIC<br>DB / DL - SSOP<br>DGG - TSSOP<br>FP - PLCC<br>N / P - PDIP<br>NS - SOP                           |    |     |     |    |   |

| Optional Carrier Suffix | LE* - Left-end taped and reeled<br>R - Taped and reeled                                                           |    |     |     |    |   |

---

JTB SEMINARDATATRANSINTRO.PPT

Tip —

■ European Mixed Signal & Logic Products

**Basics

and

Practical Examples

of Transmission**

EH9550/14801/00/E

### **Basics and Practical examples of Data Transmission**

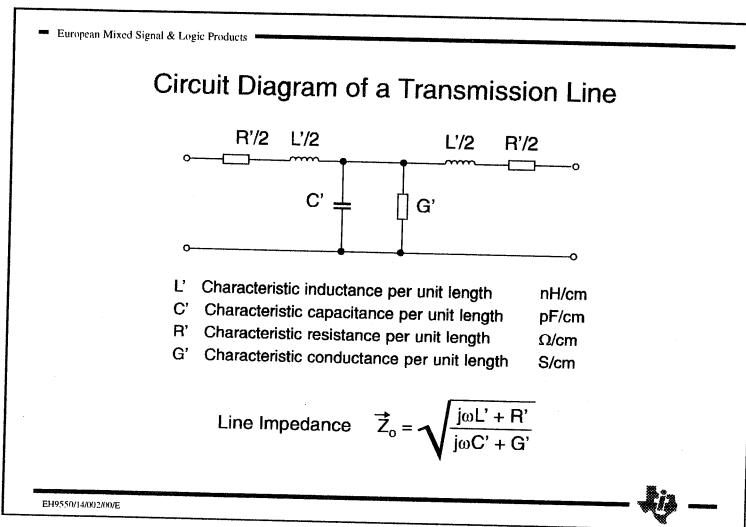

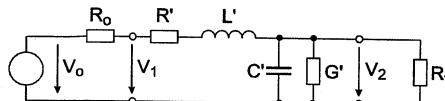

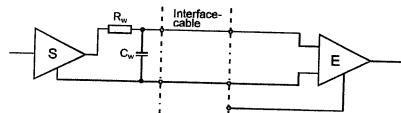

#### **Circuit diagram of a Transmission Line (14002)**

The equivalent circuit of a transmission line consists of an inductance  $L'$  - representing the inductance of the transmission line -, a resistor  $R'$  - representing the ohmic resistance of the line, a capacitance  $C'$  - representing the capacitance of the line - and the conductance  $G'$  representing the losses in the capacitance of the line. All these values are length dependent and are therefore specified in unit/length, e.g.: nH/cm, pF/cm,  $\Omega/\text{cm}$ , and S/cm. By setting up a set of differential equations, one can calculate the impedance of a transmission line:

$$Z_o = \sqrt{\frac{j\omega L' + R'}{j\omega C' + G'}}$$

In practice this equation is difficult to handle. First the line impedance results in a complex number which makes the required calculations time consuming. Second the line impedance is frequency dependent. This fact becomes uncomfortable in digital circuit, where one has to consider many frequencies simultaneously.

European Mixed Signal &amp; Logic Products

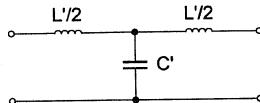

### Loss-free Transmission Lines

At high frequencies the transmission line losses ( $R'$ ,  $G'$ ) can be neglected compared with the impedance of the inductance and the conductance of the capacitance.

With  $R' \ll j\omega L'$  and  $G' \ll j\omega C'$ :

$$\text{Line impedance } Z_o = \sqrt{\frac{L'}{C'}} \quad (\text{real number!})$$

$$\text{Propagation time } t_p = \sqrt{L' \times C'}$$

EHB550/14/003/00/E

### Loss-Free Transmission Lines

In digital circuits low frequencies are not generally of concern. At higher frequencies (above some 10 kHz) the impedance of the inductance  $j\omega L'$  becomes large compared to the resistance  $R'$  of the wire. The admittance  $j\omega C'$  is also much greater than the corresponding conductance  $G'$ . Under this assumption  $R'$  and  $G'$  can be neglected. The impedance of the transmission line can now be calculated by the simple formula

$$Z_o = \sqrt{\frac{L'}{C'}}$$

The impedance is now a real number which can be handled like an ohmic resistor. A further advantage is  $Z_o$  is now independent of the frequency.

An important parameter in data transmission circuits is the propagation time  $t_p$  of the signal on a transmission line. This time is also determined by the parameters of the line:

$$t_p = \sqrt{L' C'}$$

On typical cables used in transmission circuits (coaxial cable, twisted pair cable) the propagation time becomes  $t_p = 5 \text{ ns/m}$ . This reflects a propagation speed  $v = 200\,000 \text{ km/s}$  (about 60 % of the speed of light)

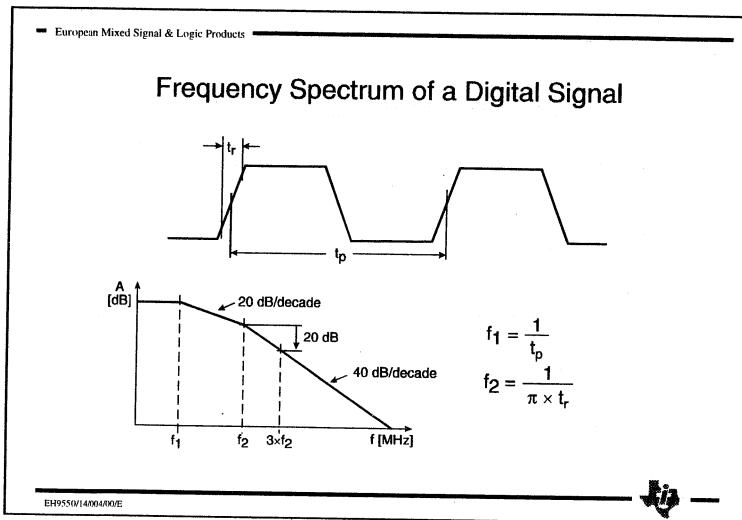

### Frequency Spectrum of a Digital Signal (14004)

The frequency spectrum of a signal is first determined by the repetition rate of the signal  $f_1$ . Above this frequency the amplitude of the overtones drops with 20 dB/decade until a frequency  $f_2$  which is determined by the rise of the signal  $t_r$ :

$$f_2 = \frac{1}{\pi \cdot t_r}$$

Assuming the bit rate to be 1 MBit/s, and the rise time of the signal to be  $t_r = 5$  ns, the frequencies are as follows:

$$f_1 = 500 \text{ kHz} \text{ (50 \% of the bit rate)} \text{ and } f_2 = 64 \text{ MHz}$$

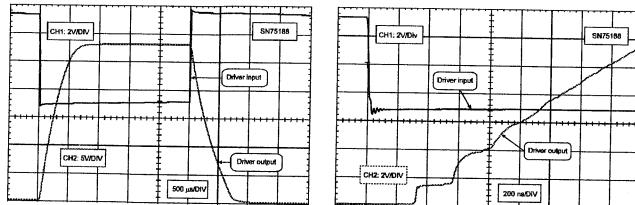

If electromagnetic interference of a transmission system is of concern, the designer can improve the compatibility by either reducing the voltage swing, reducing the data rate, or by selecting interface circuits which provide output signals with a slow rise/fall time.

■ European Mixed Signal & Logic Products ■

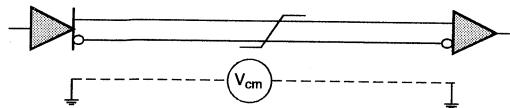

### Transmission Line

The diagram shows a horizontal line with two vertical branches at each end. The top branch is labeled "Signal line" and the bottom branch is labeled "Signal return line". At the left end, there is a small triangle labeled "Transmitter". At the right end, there is a small triangle labeled "Receiver".

A transmission line consists of

- a signal line which carries the signal current

- a signal return line (mostly ground) which carries a return current of the same magnitude.

Any DC interconnect between the GND terminals of the two circuits (e.g. safety earth) will not provide a signal return path according to the laws of the transmission line theory.

The A area between the signal line and the return line determines the capability of the circuit to radiate RF and also its susceptibility to EMI.

The diagram shows a rectangular loop representing a transmission line. Inside the rectangle, there is a diagonal line from the top-left corner to the bottom-right corner, forming a triangle. The angle between this diagonal line and the bottom edge of the rectangle is labeled  $\theta$ . The area of the triangle is labeled  $A$ . A current arrow labeled  $I$  points along the top edge of the rectangle. To the left of the rectangle, there is a small circle containing a dipole antenna symbol. Below the rectangle, the formula  $E = k \times I \times A \times \frac{1}{r} \times \sin \theta$  is written.

$$E = k \times I \times A \times \frac{1}{r} \times \sin \theta$$

BH5501400500E

### Transmission Line (14005)

The designer has to keep in mind that a transmission system always has two conductors: the signal line and the signal return line. Both lines have to be designed carefully to ensure the required quality of the interface circuit. Some random signal return path (e.g. via the protective ground wire) is not an adequate signal return line.

Both wires - the signal wire and the signal return wire - act as an antenna which influences the electromagnetic compatibility of the interface circuit. The larger the area between these wires, the larger will be the probability that electromagnetic energy is radiated, which may influence the function of neighbouring equipment. Similarly the area between these wires also determines the electromagnetic susceptibility of the interface circuit.

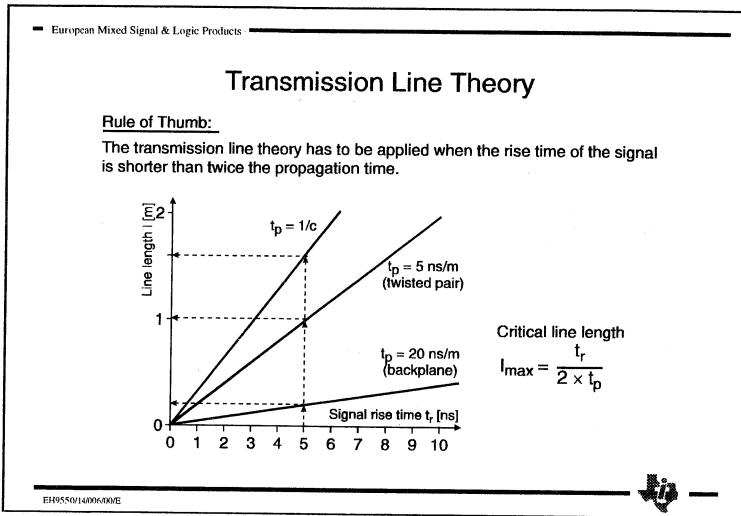

### Transmission line theory (14006)

Transmission lines have to be treated as lines in accordance with transmission line theory when twice the signal propagation time becomes longer than the rise time of the signal - i.e.: when the line reflections no longer fall anymore into the rise time interval. For a given rise time  $t_r = 5 \text{ ns}$  and a typical propagation time of the signal  $t_p = 5 \text{ ns/m}$ , the critical line length is  $I_{\max} = 1 \text{ m}$ . In applications where the propagation time of the signal is much longer - e.g. bus lines - the critical line length is even shorter.

■ European Mixed Signal &amp; Logic Products

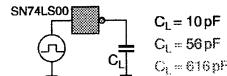

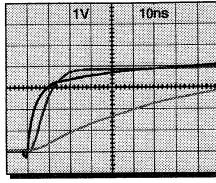

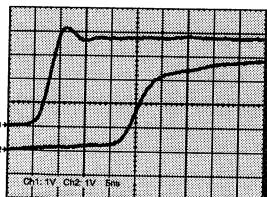

## Waveforms with Transmission Line and Capacitance Loads

EH9550/14/007/00E

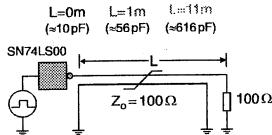

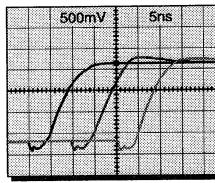

### Wave-forms with Transmission line and Capacitance Loads (14007)

Transmission line theory says that the line impedance is independent of the line length. As a consequence, the loading of the integrated circuit connected to a transmission line must be independent of the line length. The oscillogram above shows the signal wave-forms measured at the output of an integrated circuit (SN74LS00) when terminated transmission lines of various lengths ( $L = 0\text{ m}$ ,  $L = 1\text{ m}$ ,  $L = 11\text{ m}$ ) are connected to the output of the circuit (the line termination is required to avoid line reflections). The three signals measured are displayed with a time offset for visibility. In all cases the rise time of the signal - and that means also the propagation delay time of the integrated circuit - is not influenced by the line length - say: by the capacitance of the line. The designer however has to consider the propagation time of the signal on the transmission line: a line length  $L = 11\text{ m}$  results in signal propagation time  $t_p = 55\text{ ns}$ .

A simple capacitive load caused a high input capacitance of the following circuit - e.g. when driving the gate of a MOS power transistor (Miller effect) - in conjunction with the output impedance of the gate ( $R_o \approx 150\Omega$  for a SN74LS00) generates a low-pass filter, which increases the propagation delay time of the circuit.

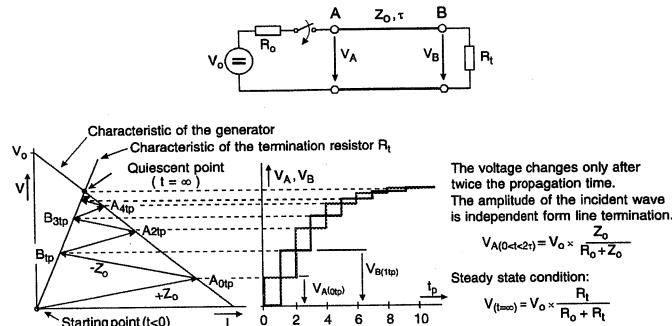

### Analysis of Line Reflections (14008)

In data transmission systems the designer has to take care of line reflections caused by improperly terminated lines. These line reflections may lead to an additional signal distortion which cause incorrect detection of the value of the signal at the line end (receiver input). This may result in a false operation of the system.

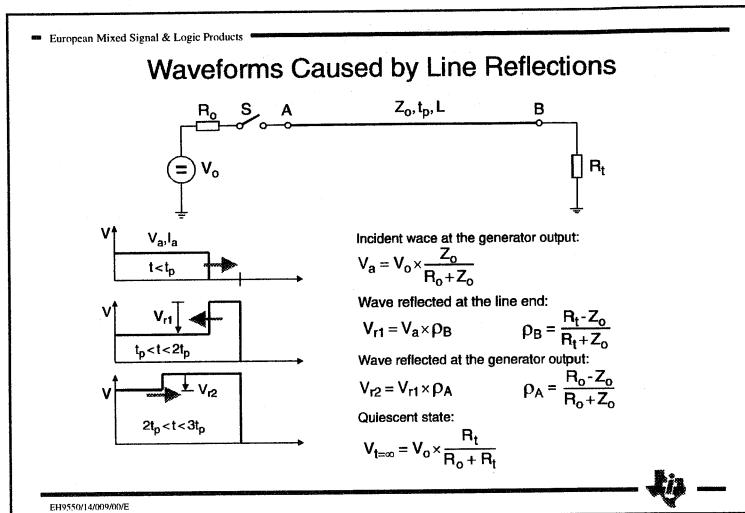

### Wave-Forms Caused by Line Reflections (14009)

The circuit above shows a simple circuit arrangement to analyse the wave-form in transmission circuits. At the time the switch at the output of the voltage source (generator) is closed, the effective generator load is the impedance of the transmission line alone. The voltage of the incident wave  $V_{a(t=0)}$  can be calculated by using the simple voltage divider formula:

$$V_{a(t=0)} = V_o \frac{Z_o}{Z_o + R_o}$$

When the wave with this amplitude arrives at the line end, the energy not absorbed in the termination resistor - assuming that the line is not terminated correctly ( $R_t \neq Z_o$ ) - will be reflected back to the generator. The amplitude of the reflected wave at that point is calculated:

$$V_{r1} = V_a \cdot \rho_B = V_a \frac{R_t - Z_o}{R_t + Z_o}$$

When this reflected wave arrives again at the generator output and the output impedance of the generator is not equal to the line impedance ( $R_o \neq Z_o$ ), again a reflection occurs, where the amplitude of the reflected wave has to be calculated:

$$V_{r2} = V_{r1} \cdot \rho_A = V_a \frac{R_o - Z_o}{R_o + Z_o}$$

This process is continued until the energy of the wave is absorbed by the losses of the circuit (termination resistor  $R_t$  at the line end, and output resistor of the generator  $R_o$ ). The final steady-state condition is calculated by the simple voltage divider:

$$V_{t=\infty} = V_o \frac{R_t}{R_o + R_t}$$

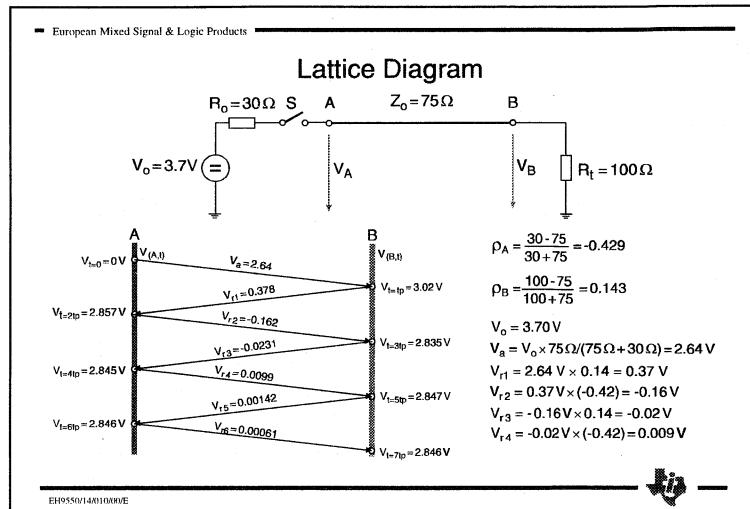

### Lattice Diagram (14010)

This example shows the analysis of an actual circuit. The generator with an open loop voltage  $V_o = 3.7 V$  and an output impedance  $R_o = 30 \Omega$  represents the simplified equivalent circuit of a SN74F00 in the high state. The line with an impedance  $Z_o = 75 \Omega$  may be a coax cable or a printed wire on multi-layer printed circuit board. As one can see, the amplitude of the reflected wave drops very fast. In most application the calculation of the various reflected waves can be stopped after the third reflection since the amplitude of the reflected wave is now so small that it can be neglected (in this example  $V_{r3} = 0.02 V$ ).

The Lattice Diagram is a useful tool to simplify handling the many numbers to be considered when analysing line reflections. In this simple example the diagram consists of two time scales, each representing the situation at the beginning and at the end of the line. A change of voltage at the generator output is found at every even multiple of the propagation time, at the end of the line at every odd multiple of the propagation time. These points are now connected by lines which represent the forward and backward travelling waves. To each of these lines the corresponding voltage is assigned. The final task left is to add these voltages at the left side of the diagram (beginning of line) of the right side (end of line) to calculate the voltage in the system at a specific time.

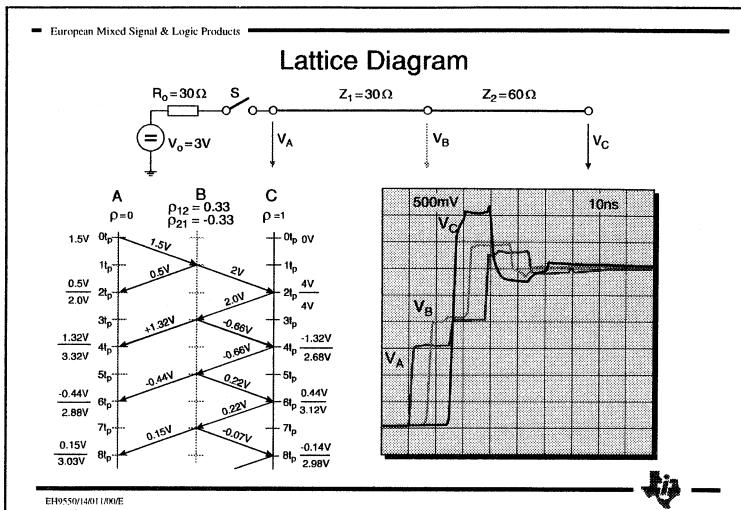

### Lattice Diagram (14011)

This picture shows a more complex circuit, where two lines of different impedance ( $Z_1 = 30 \Omega$ ,  $Z_2 = 60 \Omega$ ) are connected in series. Situations like this can be found where resistors are not carefully arranged. Another similar situation is found when long stub lines are connected to a trunk cable. This example shows, that the Lattice Diagram can also handle complex waveforms caused by various interfering waves. The transition starts at the generator output with an incident wave amplitude of 3 V, at the line end an overshoot with an amplitude of 4 V is found, while final steady-state voltage will be 3 V.

To simplify the calculation the output impedance of the generator  $R_o = 30 \Omega$  has been made equal to the line impedance  $Z_1$ . Due to this matching the line is terminated correctly (reflection factor  $\rho = 0$ ) for waves travelling backward into the generator. This avoids reflections at this point of the circuit and eliminates the need also to consider further line reflection caused by this line reflection.

European Mixed Signal &amp; Logic Products

## Bergeron Diagram

EH9550/14/012/00/E

## Bergeron Diagram

The Bergeron Diagram is a simple tool to analyse line reflections in circuits which show non-linear characteristics e.g. semiconductor components. For the analysis one has to draw a voltage/current diagram. Into this diagram the output characteristic of the generator  $R_o$  (in this example a linear resistor) as well as the characteristic of the termination at the line end  $R_t$  has to be drawn. The point of intersection of these two lines provides already the first result: the steady state voltage. The steady-state condition on the line before the switch has been closed ( $V_{t=0} = 0$  V,  $I_{t=0} = 0$  mA) is the starting point for the construction of the waveform. Through this point (in this example the origin of the diagram) a line with the slope of the line impedance  $Z_0$  ( $\tan \alpha = Z_0$ ) is drawn. Where this line hits the line which represents the output characteristic of the generator ( $A_{0tp}$ ), one gets the voltage of the incident wave. By drawing a line with the negative slope ( $\tan \alpha = -Z_0$ ) through the point just constructed, the point of intersection ( $B_{tp}$ ) with the line representing the termination characteristic  $R_t$  provides the voltage at the line end, when the wave arrives there the first time. By further drawing lines with alternating slopes ( $Z_0$ ,  $-Z_0$ ) one finds the voltages in the circuit during the following building-up. Finally the wave-forms at the begin and the end of the line can be constructed by using the voltages found during the previous construction.

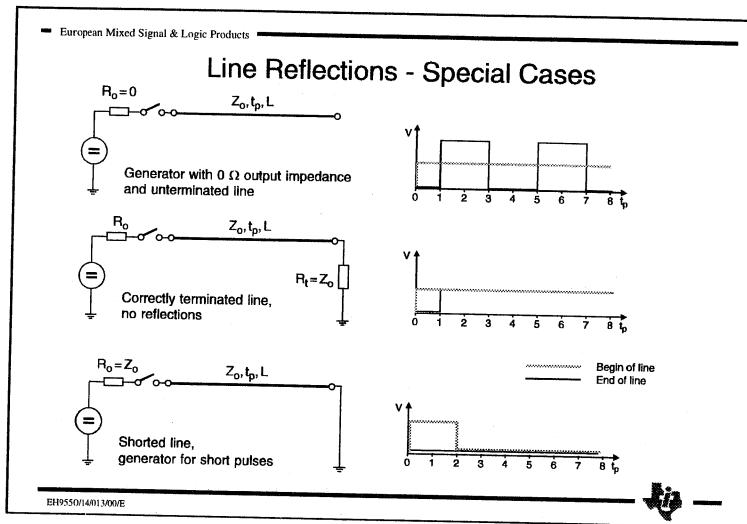

### Line Reflections - Special Cases (14013)

This picture shows various extreme situations in transmission circuits. In the first circuit a generator with zero Ohm output impedance ( $R_o = 0 \Omega$ ) drives a loss-free transmission lines, where is an open circuit at the line end ( $R_t = \infty$ ). The open circuit may represents the input impedance of integrated circuits which mostly provide an input impedance of several kilo-ohm - large compared to typical line impedance. The reflection factor  $\rho = -1$  at the generator output and  $\rho = 1$  at the line end leads to an undamped oscillation at the end of the line. That would cause a receiver to switch many times, but not once only as desired.

The next circuit shows an interface terminated correctly at the line end. Under this condition one finds an undistorted signal (no line reflections)

The last circuit shows and interface shorted at the line end. For simpler understanding the output impedance of the generator has been chosen equal to line impedance ( $R_o = Z_0$ ). When the switch is closed, an incident wave with an amplitude of  $0.5 \times V_o$  travels to the line end and is reflected there with the inverted amplitude ( $\rho = -1$ ). When the reflected wave arrives at the generator output again the steady-state is achieved. This circuit is a pulse generator which provides a pulse width equal to twice the propagation time of the wave on the transmission line. Such a circuit can be used advantageously when pulses with a length of a few nanoseconds only have to be generated.

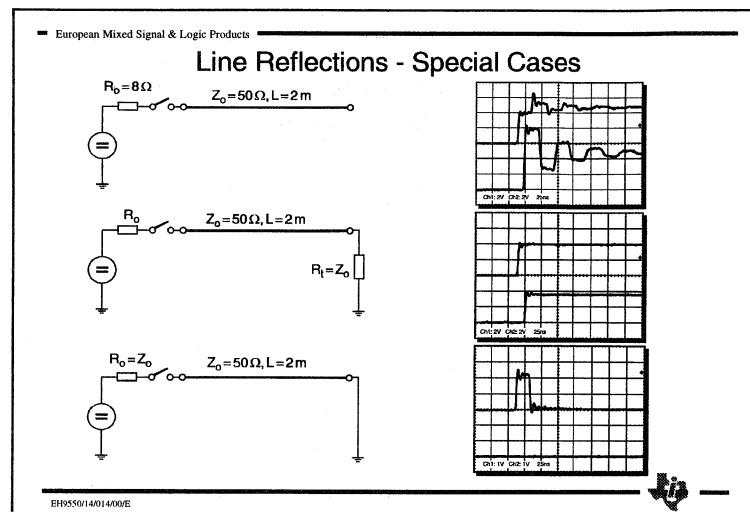

### Line Reflections - Special Cases (14014)

The circuits described before have been built up to vary the behaviour. It is not as easy to design a generator with an output impedance of  $0\Omega$ . Therefore an Advanced CMOS circuit has been used as the generator. Its output impedance  $R_o = 8\Omega$  leads to a damped oscillation, where the first undershoot at the line may still be capable to reach the threshold voltage of the receiver and to cause a false triggering.

The correctly terminated line shows no signal distortion.

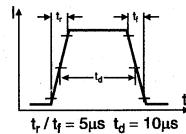

In the interface shorted at the end, a coax cable with a propagation time  $t_p = 5\text{ ns/m}$  and a length  $l = 2\text{ m}$  has been used. This circuit generates a pulse with a width  $t_d = 2 \times 5\text{ ns/m} \times 2\text{ m} = 20\text{ ns}$ .

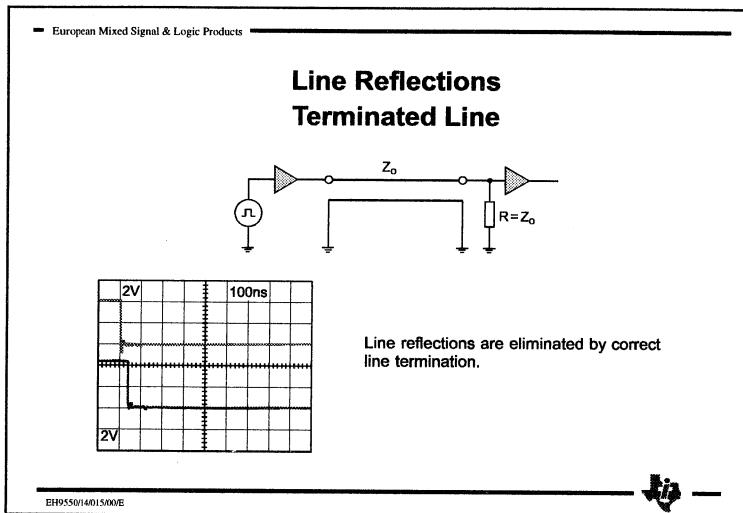

#### Line Reflections - Terminated Line (14015)

Transmission lines are terminated at the line end by a resistor between the signal line and the signal return line. If the termination resistor is chosen equal to the line impedance ( $R_t = Z_0$ ) no line reflections are found. In many applications, a mismatch of up to 50 % is acceptable. Under this condition the resulting reflection factor will be  $\rho = 0.2$ .

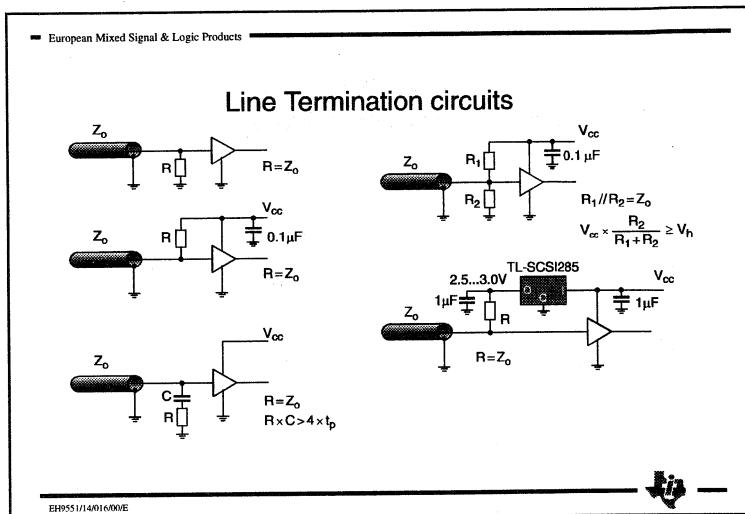

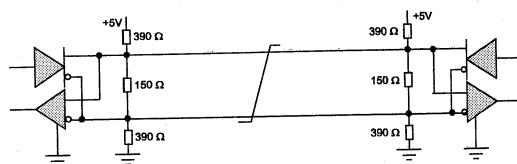

### Line Termination Circuits (14016)

Single ended or unbalanced transmission lines are usually terminated by a resistor between the line end and signal ground. If the drive capability of the generator in high state is not sufficient - e.g. circuits with open collector or open drain outputs - the termination resistor can also be placed between the line and the positive supply rail. This rail for low frequencies is shorted to ground via the power supply and for high frequencies via the decoupling capacitor (typical 0.1  $\mu$ F).

Particularly in CMOS applications, the designer does not like the continuous current in the termination resistor. This current increases the power dissipation. The current can be blocked by placing a capacitor  $C_b$  in series to the termination resistor  $R_t$ . When the time constant  $R_t \times C_b$  is about 4 times the propagation time of the interface circuit, the line is almost sufficiently terminated.

In TTL systems, a resistor divider is often found at the line end (split resistor or Thevenin termination). This circuit is adapted ideally to the drive capability of TTL circuit and performs well in terms of eliminating line reflections. However the disadvantage of this arrangement is the large DC current through the resistor divider.

In advanced interfaces therefore often a circuit is used, which is called Active Termination. Here the termination resistor is placed between the line end and the output of an additional power supply, which provides an output voltage of 2.5 ... 3 V. Since on average 50 % of its active time the line is in the high state, the supply current is reduced by this amount. This termination technique is also used in bus applications, where much of the operating time all bus drivers are in inactive mode (3-state). In this situation the supply current becomes zero. Last but not least, the pull-up resistor avoids the line floating when all bus drivers are in the 3-state.

■ European Mixed Signal & Logic Products

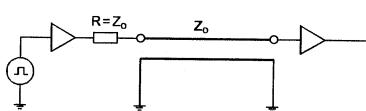

### Line reflections Matching of Generator Impedance

Under- and overshoots are avoided by matching the output impedance of the line driver to the line impedance by means of a series resistor

Power dissipation is not increased.

Note: Undefined logic levels along the transmission line occurs for up to twice the propagation time.

2V 100ns 2V

EH9551/14017A00/E

### Line Reflections - Matching of Generator Impedance (14017)

An elegant method to avoid under and overshoots at the line end is to match the output impedance of the driver circuit to the line impedance by placing a resistor in series with the output. A different output impedance of the driver in the low and the high state mostly does not allow correct matching. As long as the output impedance of the circuit in question is chosen to be 60 % to 100 % of the line impedance, a reasonable signal quality can be expected at the line end (receiver input). This technique is applicable in uni- and bi-directional point to point interfaces. In multi-point applications, where several stations are located along the transmission line, this technique is not recommended due to the long settling time of the signal (up to twice the propagation time).

European Mixed Signal &amp; Logic Products

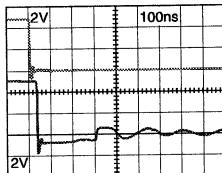

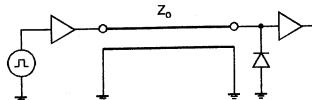

### Line Reflections Clamping Diodes

Clampind diodes at the end of the transmission line absorb the energy of under- and overshoots and ensure a clean signal waveform.

Input circuits of logic IC's contain these clamping diodes.

EH251/1401800/E

### Line Reflections - Clamping Diodes (14018)

An effective method to avoid excessive under- and overshoot at the line end is to limit this by means of clamping diodes. As the picture shows, a negative transition at the begin of the transmission line causes a negative undershoot at the line end which amplitude is limited to the forward voltage of the clamping diode at the line end ( $\approx 0.7V$ ). The energy stored in the transmission line is not absorbed totally. Therefor one can observe several waves travelling forward and backward on the line. However its amplitude is a few 100 mV only.

Due to the positive influence of these diodes, clamping diodes are integrated into all logic circuits. TTL circuits contain at their inputs clamping diodes to the ground terminal to limit negative undershoots. In a CMOS environment, where due to the higher voltage swing also the positive overshoots are of concern, mostly additional clamping diode between the input and the positive supply rail are incorporated.

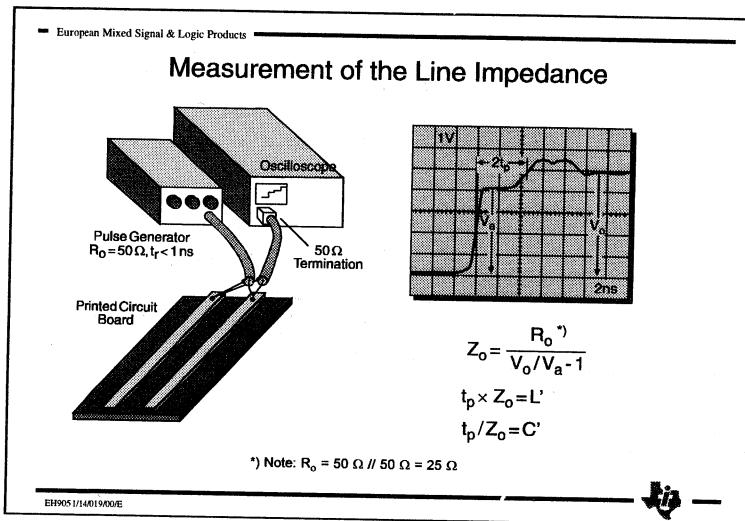

### Measurement of the Line Impedance (14019)

For a correct design of an interface (selection of the generator, termination of the transmission line), knowledge of the impedance of the transmission line in use is necessary. One way to determine the line impedance is by means of a L/C bridge where one measures the inductance of a transmission line shorted at the end (short circuit impedance  $\approx$  inductive layer  $L'$ ) and capacitance with the line open at the end (open circuit impedance  $\approx$  capacitive layer  $C'$ ). This method however mostly requires expensive equipment which often is not available.

A simpler method is shown on the picture above, where one needs a fast pulse generator and an oscilloscope only. By applying this method one measures the amplitude of the incident wave  $V_a$  caused by the voltage divider 'output impedance of the generator / line impedance' (in this example a signal and a ground wire in parallel on a printed circuit board) as well as the steady-state voltage  $V_o$ . By using the following equation (the voltage divider formula solved to  $Z_o$ ) one gets the line impedance  $Z_o$ :

$$Z_o = \frac{R_o}{\frac{V_o}{V_a} - 1}$$

where  $R_o$  is output impedance of the generator. In this measurement set up the output impedance is made by the two coax cables in parallel, therefore  $R_o = 25 \Omega$ .

By measuring the propagation time  $t_p$  one can also determine the inductance and the capacitance per unit length:

$$L' = t_p \cdot Z_o \quad C = \frac{t_p}{Z_o}$$

European Mixed Signal &amp; Logic Products

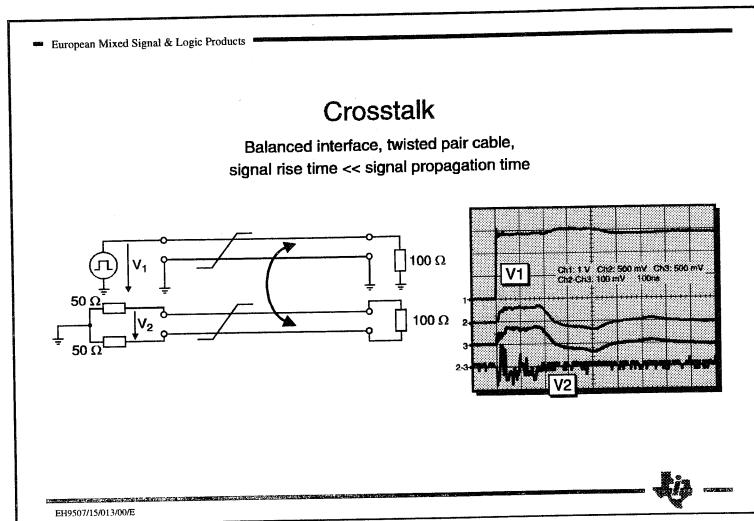

## Crosstalk

On long transmission lines ( $2 \times t_p > t_r$ ) the crosstalk can be calculated as follows:

BH9051/14/02000/E

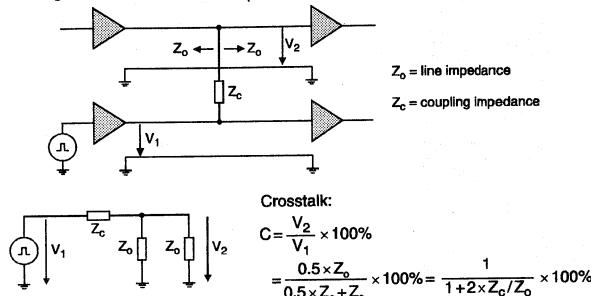

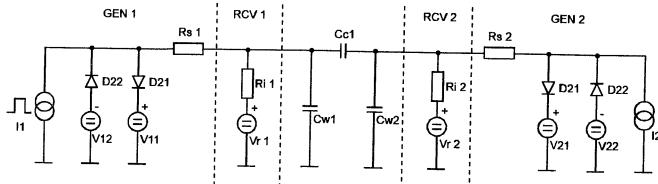

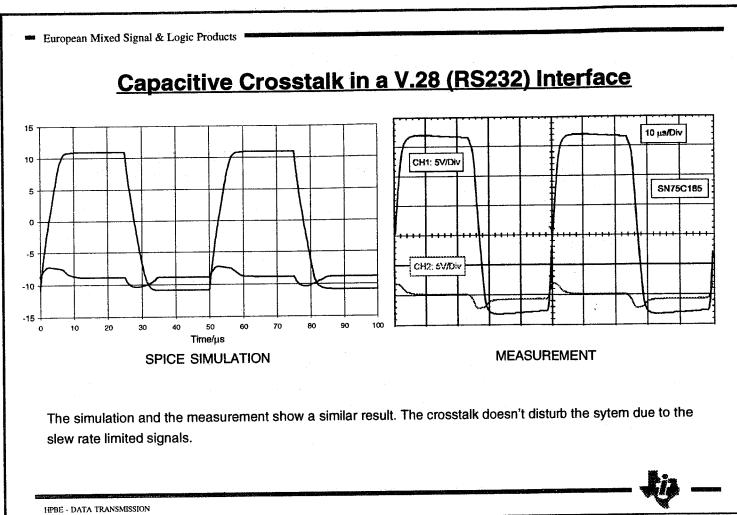

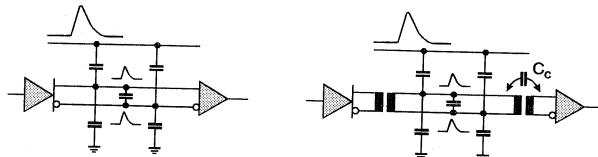

### Crosstalk (14020)

The characteristic of a transmission line can be described by its inductance and capacitance per unit length. When two transmission lines are placed in parallel, one can now define inductance and capacitance per unit length between these two circuits, to give the coupling impedance  $Z_c$ . Using this assumption, one can easily describe the crosstalk between interfaces: A signal is transmitted via one line and is coupled via the coupling impedance into the neighbouring line. At the point of coupling the load for the cross-coupled signal is half of the line impedance  $Z_o$  (two lines running in opposite direction). The resulting crosstalk can now be calculated by using the following formula:

$$C = \frac{1}{1 + 2 \frac{Z_c}{Z_o}}$$

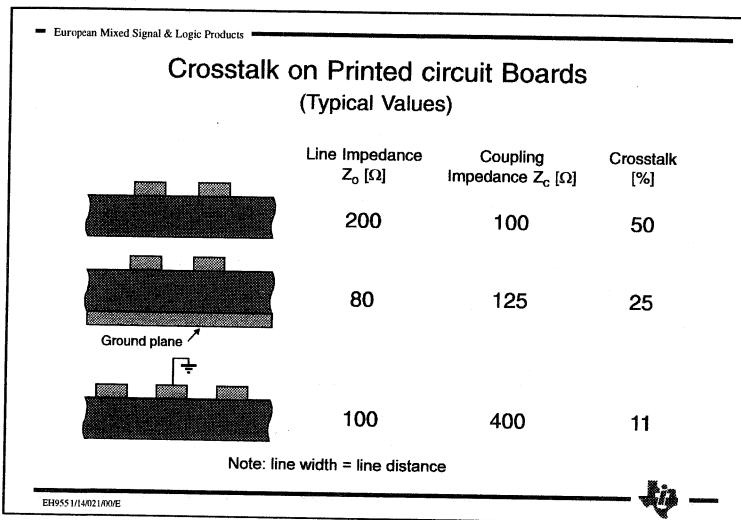

### Crosstalk on printed circuit boards (14021)

By applying the formula above, the crosstalk between signal lines on printed circuit boards can be analysed. In the first example two printed wires are running in parallel, with the width of the wires equal to the distance between the wires e.g. 0.5 mm. This arrangement results in a coupling impedance  $Z_c = 100 \Omega$ . (In the literature dealing with strip lines and microstrips, formulas are shown which allow the calculation of the line impedance based on the physical dimension of the lines). The ground return line is assumed to be far away e.g. 2 cm. This leads to a line impedance of  $200 \Omega$  and a crosstalk  $C = 50\%$ . Since no logic circuit provides a noise margin of 50 %, such an arrangement is not applicable.

In the second example a ground plane is placed on the opposite side of the printed circuit board. By this the line impedance is lowered to  $Z_o = 80 \Omega$ , the coupling impedance is increased to  $Z_c = 125 \Omega$ . The resulting crosstalk is now only 25 %. In digital circuits such value may be acceptable. This example also explains the benefit of a multi layer-board with a ground plane in terms of lowering the noise level in digital circuits.

In the third example a shielding wire is placed between the signal lines. (Note: The shielding wire must be connected to ground on both ends.) Again it is assumed, that the line width is equal to line separation. In such an arrangement the line impedance becomes  $Z_o = 100 \Omega$  and the coupling impedance  $Z_c = 400 \Omega$ . The resulting crosstalk is lowered to  $C = 10\%$ . In digital circuits such a crosstalk is fully acceptable.

This also explains why also twisted pair cables are used for longer lines. One wire of the pair is the signal line, and the other the signal return (ground). Similar behaviour is found, if flat cables are used with alternate ground and signal lines. Such an arrangement gives a well defined line impedance ( $Z_o = 80$  to  $120 \Omega$ ) and a low crosstalk. Last but not least, typical crosstalk in a well designed interface will be at least 10 %. This is also valid for the interference between any electrical cable and the interfaces.

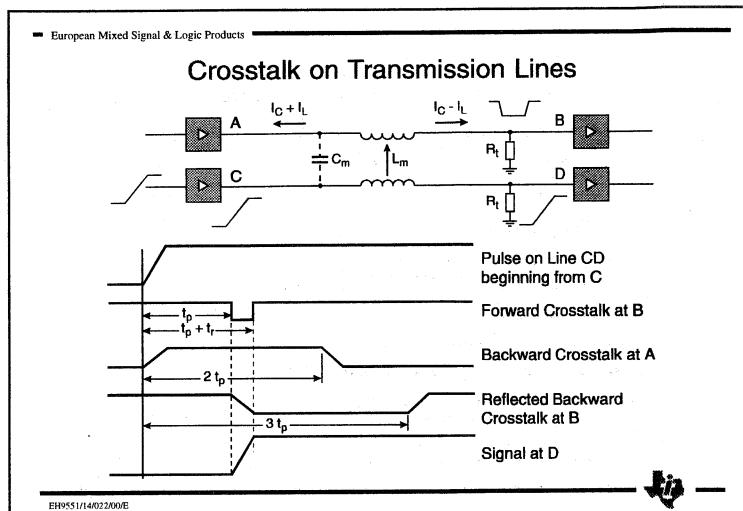

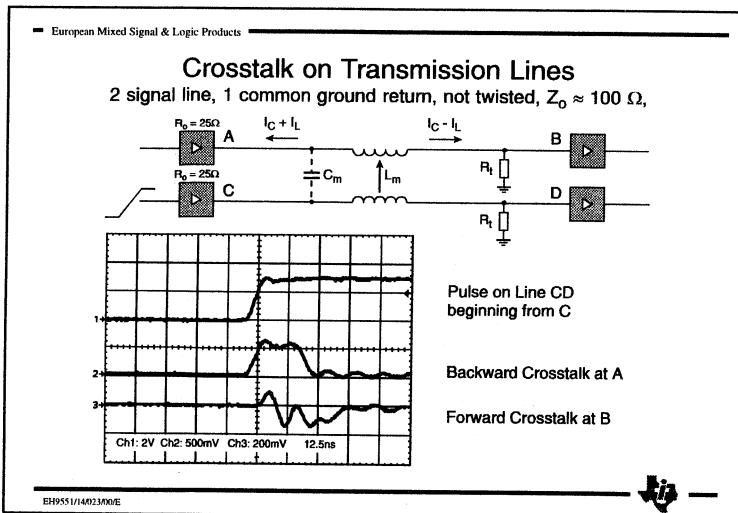

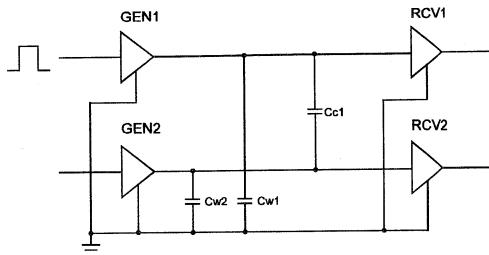

### Crosstalk on Transmission Lines (14022)

When analysing the crosstalk in more detail, one finds that it induces two currents into the affected line: A current  $I_C$  caused by the capacitive crosstalk and a current  $I_L$  caused by the inductive crosstalk. When looking from the generator standpoint, the currents travelling down the affected line subtract ( $I_C - I_L$ ). This results at the end of this line in a relatively small negative noise pulse with a width equal to the rise time of the original signal (forward crosstalk at B in the picture above). In the reverse direction the currents add ( $I_C + I_L$ ), which leads at the line end near to the generator to a pulse which width is equal to twice the propagation time of signal (Backward crosstalk at A in the picture above). This noise pulse is reflected at the point A and arrives after one propagation time at the far end (Reflected backward crosstalk at B in the picture above).

### Crosstalk on Transmission Lines, 3-wire Cable (14023)

In the following, the behaviour of various circuits arrangements will be analysed. In the first example a transmission line with length 2 m is used which consists of three wires running in parallel (not twisted). The crosscoupled signal at the point B has again a relatively small amplitude which is superimposed on the noise caused by the reflected backward crosstalk at B. Since the generator output impedance at A is smaller than the line impedance, the reflection factor at A becomes negative. This results in a negative amplitude of the forward crosstalk at B.

Note that the three wire circuit used in this application has a similar characteristic to the printed wire circuit with a shielding wire between these two lines (discussed above). The crosstalk is relatively small. In a multi core cable, where only one or a few ground return wires are available, the crosstalk becomes much larger. Under these conditions, reliable operation of the interface can no longer be guaranteed.

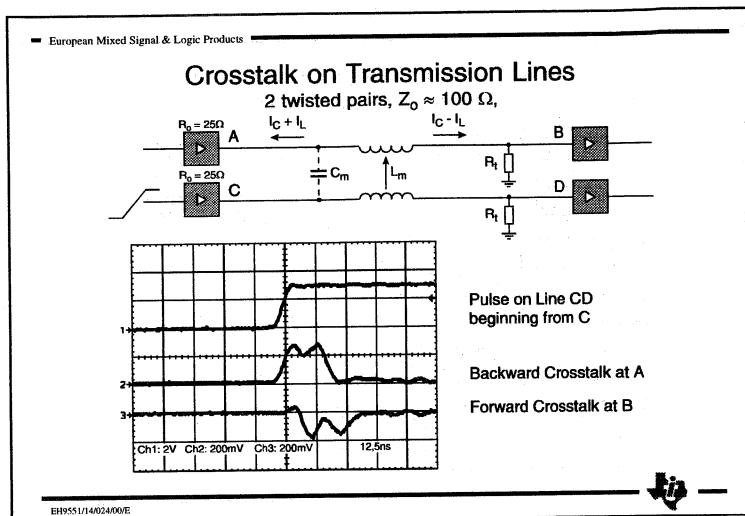

### Crosstalk on Transmission Lines, Twisted Pair Cable (14024)

The same circuit arrangement, but using twisted pairs, shows a similar behaviour. The crosstalk at the far end (the receiver at the induced line) again is relatively small. When using twisted pair cables the shielding effect of the many signal return wires keeps the crosstalk at moderately low level even if many pairs are running in parallel in cable.

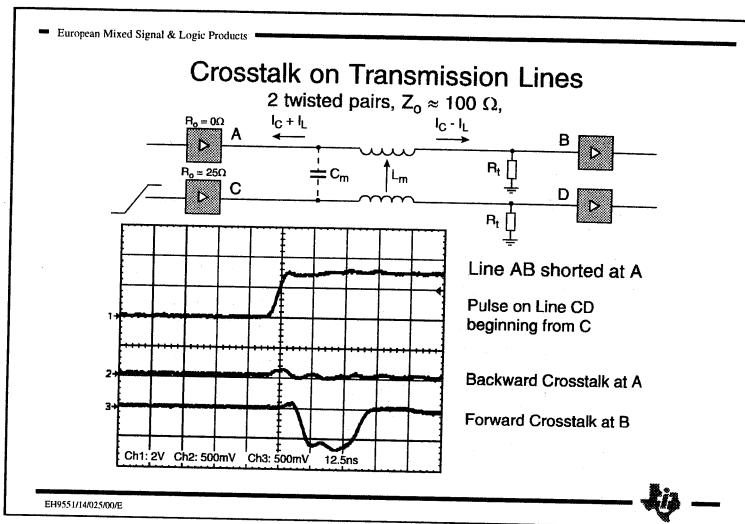

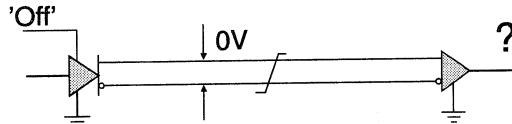

### Crosstalk on Transmission Lines, Near End Impedance = 0 (14025)

It has been shown that the forward crosstalk at the point B is determined to a large degree by the crosstalk reflected at the point B. In the picture above the output impedance of the generator of the affected line is made to zero. Therefore the resulting reflection factor at this point becomes  $\rho = -1$ . Due to a higher amplitude reflected at this point, the forward crosstalk at the point B also becomes larger. However this example shows an extreme situation. In practise the output impedance of the generator is between 10 and 100 % of the line impedance. This will result in a reflection factor  $\rho < -1$ , and therefore to a crosscoupled voltage which is significantly smaller.

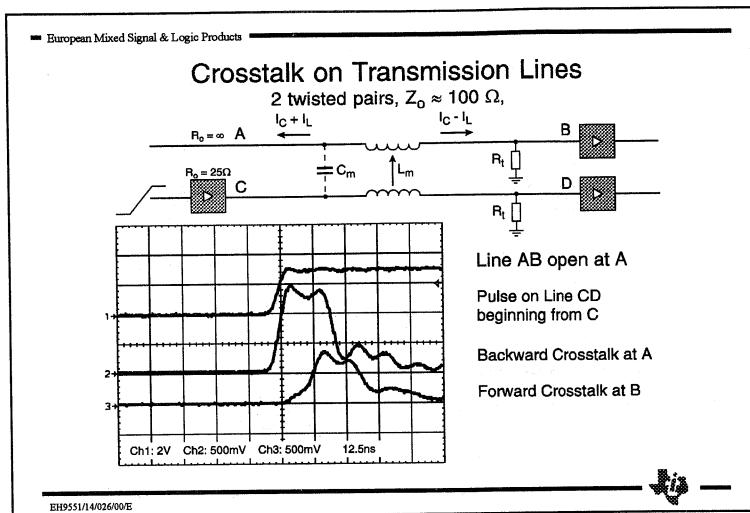

#### Crosstalk on Transmission Lines, Near End Impedance = $\infty$

If the output impedance of the generator at the affected line becomes very large (e.g. generator output in 3-state), the reflection factor becomes  $\rho = 1$  (positive!). Thus the crosscoupled signal has a large positive amplitude at the point A. This leads also to a positive amplitude of the noise voltage at the point B. Note the magnitude of the noise voltage at the point B is the same as in the previous example, only the sign of the voltage is different.

Consider also the following situation: Assuming a receiver is located at B where the line is not terminated, the function of the receiver may be affected by the large noise voltage there. (Backward crosstalk at A in the picture above)

— European Mixed Signal & Logic Products —

### Losses on Transmission Lines

$$V_2 = V_1 \times e^{-\frac{R'}{2Z_o}l}$$

Due to the skin effect at frequencies above some hundred kHz only the outer layer of the wire conducts. Thus the losses increase by a factor  $\sqrt{f}$ .

| f (MHz) | $\vartheta$ ( $\mu\text{m}$ ) |

|---------|-------------------------------|

| 1       | 68                            |

| 100     | 6.8                           |

| 10,000  | 0.68                          |

EH9551/14/027/00/E

### Losses on Transmission Lines

Owing to the ohmic resistance of the wires  $R'$ , and to a lower degree the conduction  $G'$  of the transmission lines, the amplitude of the signal is degraded with increasing line length. The voltage at the line  $V_2$  can be calculated by using the following formula:

$$V_2 = V_1 \cdot e^{\frac{-R' \cdot l - G' \cdot l \cdot Z_o}{2 \cdot Z_o}}$$

with  $G' \rightarrow 0$  one can simplify the equation:

$$V_2 = V_1 \cdot e^{\frac{-R' \cdot l}{2 \cdot Z_o}}$$

As an example, a transmission line with impedance  $Z_o = 100 \Omega$ , length  $l = 1000 \text{ m}$  and resistance per unit length  $R' = 0.1 \Omega/\text{m}$ , reduces the voltage at the line end by about 40 %.

The formula shown above does not consider the so-called Skin Effect. This causes the current to flow only on the surface of the conductor at higher frequencies. This becomes of importance at frequencies  $> 100 \text{ kHz}$ .

Therefore above this frequency the resistance of the wire increases with  $\sqrt{f}$ .

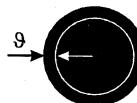

### Frequency response of a Transmission Line (14028)

Due to the skin effect, a transmission line has a characteristic similar to a low-pass filter. To analyse the actual behaviour of a transmission line, we measured a twisted pair cable of length  $l = 20 \text{ m}$  and conductor diameter  $d = 0.6 \text{ mm}$ . As can be seen in the picture above, up to a frequency of 1 MHz the losses of the cable remain small. Above 1 MHz however, the attenuation increases considerably.

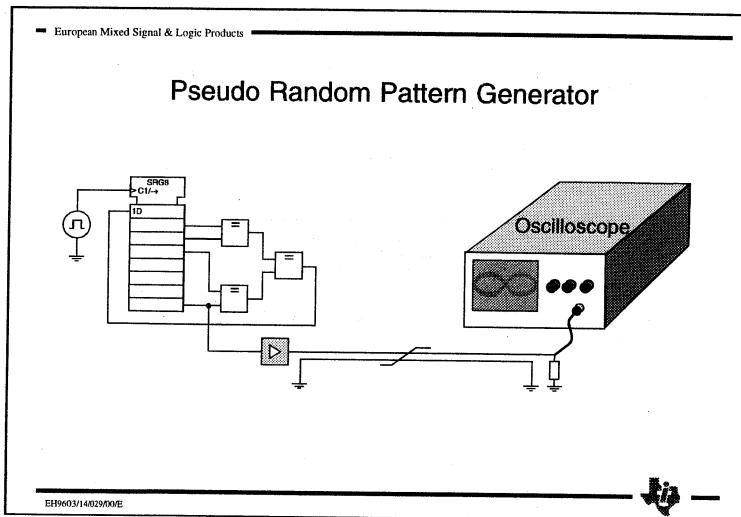

#### Pseudo-Random Pattern Generator (14029)

In data transmission circuits we have to consider not only discrete frequencies, but a wide frequency band determined by the bit pattern of the data transmitted. Long sequences of ones or zeros represent a low frequency, alternating bit carrying ones and zeros represent a high frequency. Due to the DC content in longer steady states and the filter characteristic of longer lines a DC shift of the average voltage is generated on the transmission line. This DC shift causes the effective amplitude of the signal and the required threshold voltages of the receiver to fluctuate.

To analyse the characteristic of transmission lines therefore a random pattern bit stream has to be applied to the input of the cable while observing the response at the end of the lines. A pseudo random pattern generator can be made easily by a shift register with a feedback from some of the outputs to the serial inputs via an Exclusive OR function. When selecting the correct feedback path the repetition period of this generator is  $2^n - 1$  shift clock cycles, where n is number of bits in the shift register. The picture above shows such a pseudo ransom pattern generator with an 8-bit shift register. The repetition period in this examples is  $2^8 - 1 = 255$  shift clock cycle.

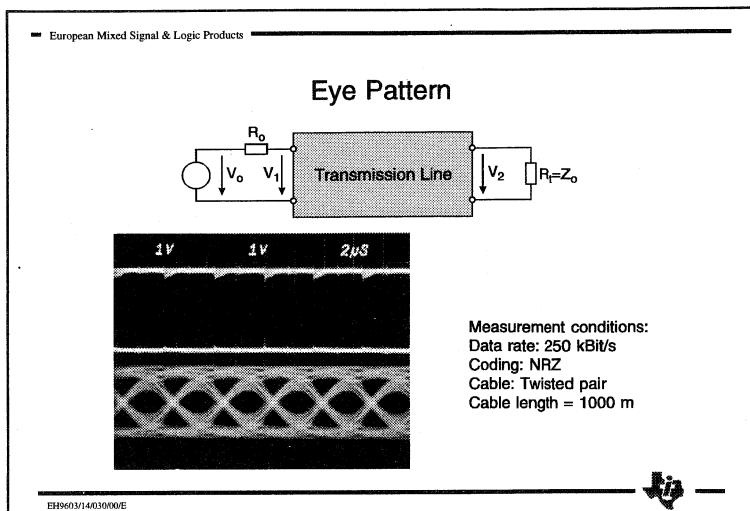

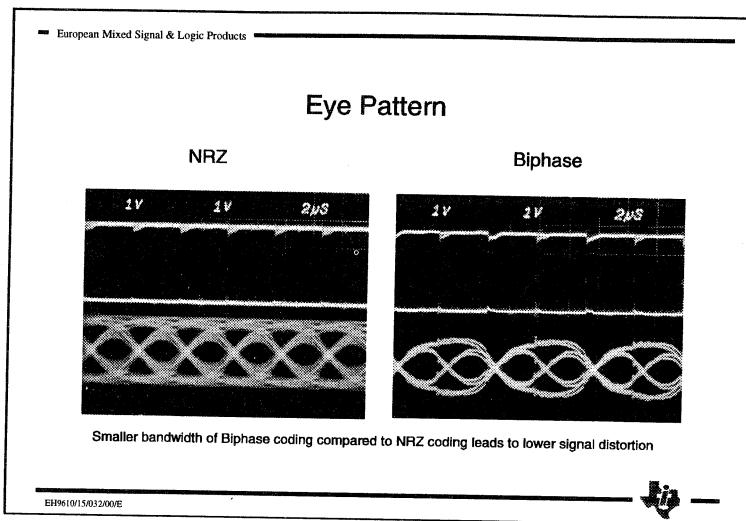

### Eye Pattern (14030)

Using the pseudo random pattern generator described above, the transfer characteristic of a twisted pair cable has been tested. The cable has length  $l = 1000$  m and wire diameter  $d = 0.6$  mm. The data rate is  $r \approx 300$  kBit/s (bit duration  $\approx 3.5$  s). The signal at the beginning (upper trace in the above picture) is a square wave. At the line end the low-pass filter performed by the cable slows down the rise time as well as the amplitude (lower trace). The ohmic resistance of the wire has only a minor influence when comparing the peak voltages at the beginning and the end of the line.

The majority of the signal quality degradation is caused by the frequency-dependent losses (skin effect). The voltage swing and the time interval left for recovering the transmitted information is the eye-shaped window in the signal flow. The height of the window gives the effective signal amplitude which has to be detected by the receiver circuit. The width of the eye determines the final time interval in which the information has to be sampled. This picture shows also that the point of transition between the single bits varies depending on the previous bit sequence. This transition time variation is called jitter. Therefore in many receiver systems one can find a sophisticated clock recovery circuit to regenerate the original timing (clock) of the information for correct sampling of the data.

■ European Mixed Signal & Logic Products

# Protective Circuits

ESD and Latch up

EHB549/08/001/00/E

European Mixed Signal & Logic Products

## Electrostatic Discharge 1 Human Body Model (MIL Std 883)

**E = 0,4...4 μWS**

The Human Body Model simulates the discharge of a human body into an electronic device.

Questions: - Voltage? - Capacitance? - Resistor? - Rise time (5 ... 10 ns)?

Note: When it tickles the finger, the voltage is >4000 V.

The real rise time during an electrostatic discharge is <1 ns.

EH9549/08/002/00/E

### Electrostatic Discharge 1, Human Body Model (08002)

Various test methods have been developed to analyse the immunity of electronic components to damage by an electrostatic discharge. One popular test circuit is the so-called Human Body Model, which simulates the situation where the electric charge stored in a human body is discharged into the device under test. To simulate that a capacitor  $C = 100 \text{ pF}$  (capacitance of the human body) is charged up to a voltage of  $V = \pm 2000 \text{ V}$  and is discharged thereafter via a resistor  $R = 1.5 \text{ k}\Omega$  into the circuit. Despite the question as to how far this test circuit really simulates the situation mentioned some comments are necessary to explain the different modes of destruction:

- 1) Short transition time of the discharge: The transition time of the current in the circuit under test at the beginning of the discharge is extremely short:  $t_r < 1 \text{ ns}$ . During this short time interval only a small area of the total protection network inside the integrated circuit starts to conduct. This small area in some cases is not capable of dissipating the total power. The silicon melts and the device is destroyed. This phenomenon explains also that if the discharge does not occur in immediate neighbourhood of the circuit but at a certain distance the device will survive: the inductance of the interconnect between the point of discharge and the integrated circuit slows down the rise time. Now the total area of the integrated protection network can conduct and short the current to ground.

- 2) High current: The protection network must be able to carry the relative high currents during the discharge. In the test circuit shown above the peak current is  $\approx 1.5 \text{ A}$ .

- 3) High energy: The protection network must be capable to handle the energy during a discharge. Mostly however the energy is not of concern. Most of the power stored in the capacitor is dissipated in the series resistor. Assuming the breakdown voltage of the device under test to be  $V_{br} = 20 \text{ V}$  (in most applications only the forward voltage of the clamping diode  $V_f = 1 \text{ to } 2 \text{ V}$  has to be considered), the resulting Energy  $E_a$  to be absorbed by the device under test can be calculated as follows:

$$E_a = V_{br} \cdot V \cdot C = 20V \cdot 2000V \cdot 100pF = 4\mu Ws$$

European Mixed Signal &amp; Logic Products

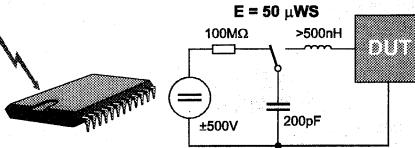

## Electrostatic Discharge 2 Machine Model

The Machine Model is a modified Human Body Model to simulate the discharge of a human body into an electronic device.

- Questions: - Voltage?                    - Resistor?

- Capacitance?                            - Rise time (20 ns)?

Today integrated circuits withstand a discharge with a voltage of 200 ... 300 V.

EH9549/08/03/00/E

### Electrostatic Discharge 2, Machine Model (08003)

Another test circuit had been developed in Japan called the Machine Model. In this test set up a capacitor of  $C = 200 \text{ pF}$  is charged up to a voltage  $V = \pm 500 \text{ V}$ , thereafter the capacitor is discharged into the device under test without any current limiting series resistor. Because of this, the energy  $E_a$  to be absorbed in the device under test becomes much larger:

$$E_a = 0.5 \cdot V^2 \cdot C = 500^2 \text{ V}^2 \cdot 200 \text{ pF} = 50 \mu\text{Ws}$$

On the other hand, the test specification allows a relatively high inductance in the discharge circuit (up to 500 nH). This inductance slows down the rise time of the discharge current. Finally, this test mostly addresses the capability of the device under test to absorb a certain amount of energy. That a fast reaction time of the protection circuit is required for fast slew rates is not so much of concern.

Last but not least, state-of-the-art integrated circuits withstand without damage a Human Body Model (2000 V; 200 pF; 1.5 kΩ), while most circuits in a Machine-Model test, they withstand only voltages up to 200...300 V.

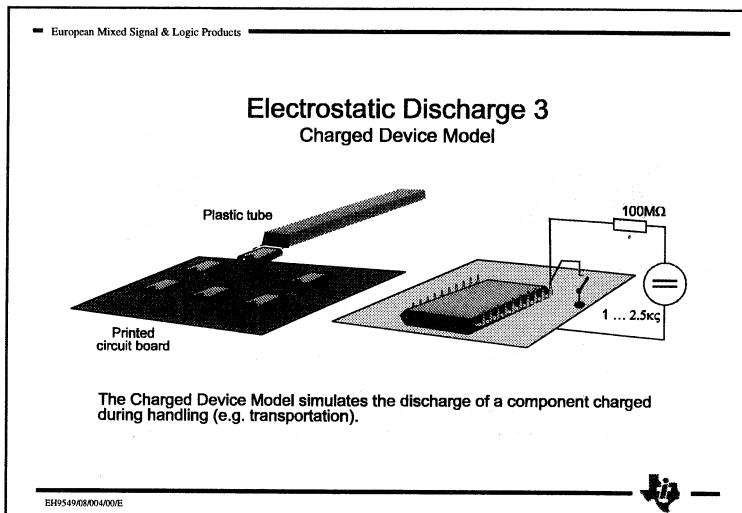

#### Electrostatic Discharge 3, Charged Device Model (08004)

Even after continuous improvement of the capability of protection networks inside integrated circuits, damaged components were still found after assembly on a printed board. A detailed investigation showed that this destruction could be explained by the following situation: In an automatic assembly equipment during assembly the integrated circuit in question slides through the plastic tube (the container during transportation and storage) and is charged up. When the circuit lands on the printed circuit board the capacitance of the device is discharged again. By this discharge, the circuit may be destroyed.

To test the immunity against discharge the device under test is placed on a metal plate (see the above figure). The circuit is charged up to a voltage  $V = 1,5$  to  $2$  kV. Thereafter the pin of the device to be investigated is shorted to the metal plate. It has been demonstrated that integrated circuits which withstand a test with a voltage  $V = 1,5$  to  $2$  kV, are not degraded during the assembly cycle. Circuits which withstand a lower voltage, may be degraded. It has to be mentioned that until now no correlation has been found between the test results of the human body model test and the charged device model test. Circuits which show a good performance in one test environment, may fail in the other one.

■ European Mixed Signal &amp; Logic Products

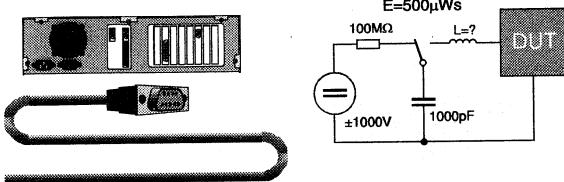

### Real World ESD Test Connection of a Charged Cable

A cable with a length of 10 m ( $C = 1000 \text{ pF}$ ) is connected to an electronic equipment. The energy stored in the capacitance of the cable is discharged into the electronic components of the interface circuitry.

EH9549/08/005/00/E

### Real World ESD Test (08005)

All the tests shown above by far do not show the rough treatment which may happen to interface circuits. A typical situation is the following: A modem needs to be connected to a personal computer. The modem is placed at one end of the room, the computer at the other end, with 10 m between these two equipments. The man who installs the cable walks through the room over carpet, which as is well-known, generates high electrostatic charge. By keeping one end of the cable in his hand, the cable may be charged up to a voltage  $V = 1000 \text{ V}$ . When the cable is now connected to the equipment, the capacitance of the cable  $C = 1000 \text{ pF}$  is discharged into the interface circuits. The energy to be absorbed under this condition is far higher than that found in the previous test standards:

$$E_a = 0.5 \cdot V^2 \cdot C = 0.5 \cdot 1000^2 \text{ V}^2 \cdot 1000 \text{ pF} = 500 \mu \text{Ws}$$

■ European Mixed Signal & Logic Products

### Temperature in a Protection Circuit

Connection of a Charged Cable

$$\Delta\vartheta = \frac{E}{V_s \times C_s}$$

$$\Delta\vartheta = \frac{500\mu\text{Ws}}{80 \times 10^{-6} \text{ mm}^3 \times 1,631 \text{ Ws/Kcm}^3}$$

$$\Delta\vartheta = 3830 \text{ K}$$

Due to the slow propagation speed of the heat ( $1 \mu\text{m}/\mu\text{s}$ ), the energy of an electrostatic discharge heats up mainly the relatively small volume of the protection circuit only.

The high temperatures generated by the high discharge energies lead to melting of the silicon and immediate destruction of the component.

bj

BH954908/006/00/E

### Temperature in a protection circuit (08006)

The protection network inside an integrated circuit has to absorb the energy during the electrostatic discharge described above. The discharge time is relatively short. In the case of the charged cable the discharge time is twice the propagation time of a wave on the cable =  $2 \times 10 \text{ m} \times 5 \text{ ns/m} = 50 \text{ ns}$ . During this time energy is injected into the protection circuit. It is further assumed that the protection circuit occupies an area of  $200 \times 200 \text{ mm}^2$  (four times the size of a bond pad), and that the depth of the junction is  $2 \mu\text{m}$ , which results in a volume  $V_s = 80 \times 10^{-6} \text{ mm}^3$ . Considering, that the thermal propagation time of the heat wave in the silicon crystal is about  $1 \mu\text{m}/\mu\text{s}$ , one can say that during the first microseconds the total heat will stay in the protection circuit. By knowing the thermal capacitance of silicon  $C_s = 1.631 \text{ Ws/Kcm}^3$ , the temperature increase  $\Delta\vartheta$  in the protection network can be calculated:

$$\Delta\vartheta = \frac{E_a}{V_s \cdot C_s} = \frac{500\mu\text{Ws}}{80 \cdot 10^{-6} \text{ mm}^3 \cdot 1.631 \text{ Ws / Kcm}^3} = 3830 \text{ K}$$

The melting temperature of silicon is about  $1600^\circ\text{C}$ . The aluminium metallization - already melted at much lower temperatures - will diffuse into the silicon. The normally high impedance ESD protection circuit becomes a short circuit.

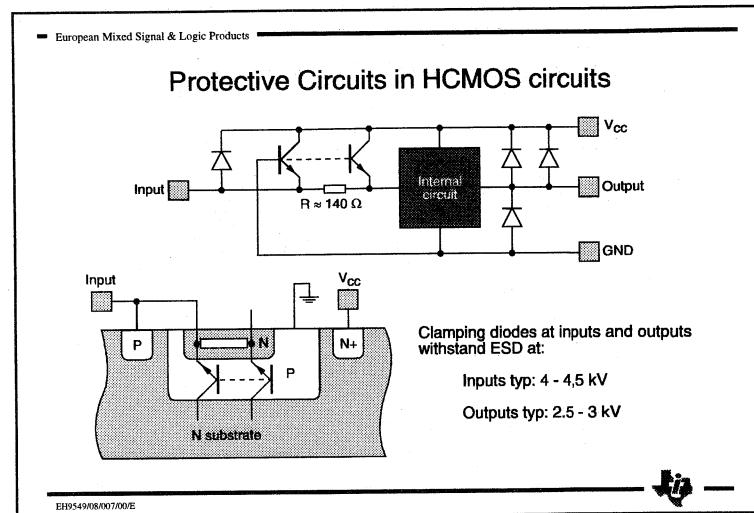

### Protective Circuits in HCMOS Circuits (08007)

The protection circuits in integrated components are of different kinds depending on the actual requirements. Bipolar integrated logic circuits for example in most cases do not require any special measures at the outputs due to the high current capability of the output transistors. These components already guarantee sufficient protection against damage by an electrostatic discharge. In CMOS circuits additional measures are required. At the output we find diodes to the positive ( $V_{cc}$ ) and negative (GND) supply rails, which in a case of a discharge lead the current to these supply rails. A second diode shown at the output and the  $V_{cc}$  terminal is a so called parasitic diode generated by the p-doped diffusion of the drain of the output transistor located in the n-doped substrate.

At the inputs of CMOS circuits we mostly find diodes to the  $V_{cc}$  rail to limit positive voltages. The limiter for negative voltages in the above circuits diagram looks like a transistor with a resistor in parallel. The original design goal was a resistor - to limit the current - and a diode - to limit the voltage -. The result is shown in the picture above: The resistor is an n-doped diffusion area placed in a p-doped tank (for isolation purpose). The total circuit again is located in a n-doped substrate. Beside the desired resistor and diode this structure also produces a so-called parasitic PNP transistor. In the case of the protection circuit this will not be any disadvantage. During an electrostatic discharge a certain amount of the current will flow via the parasitic collector also to the  $V_{cc}$  rail. That however will not degrade the quality of the circuit.

The circuit described here shall be an example only. In practice one finds a wide variety of circuits adapted to the application requirements as well to the process capabilities of the semiconductor structure.

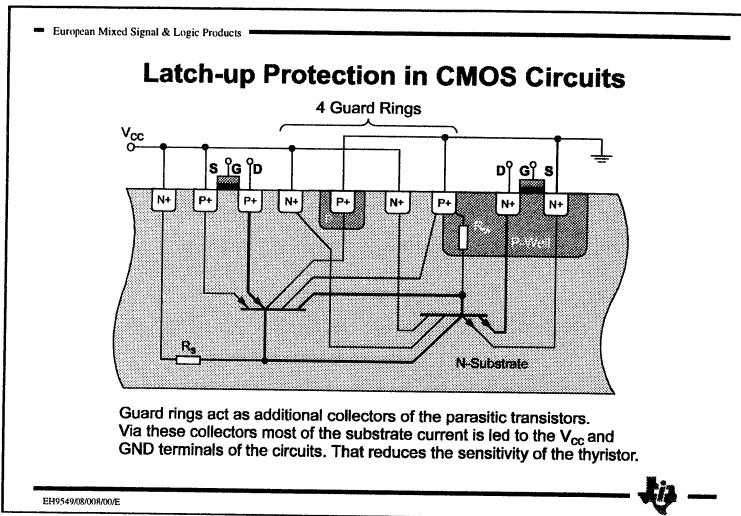

### Latch up Protection in CMOS Circuits (08008)

Whenever a semiconductor manufacturer produces complementary MOS circuits (CMOS), PNPN structures are generated on the silicon chip. In the above picture the p-diffusion of drain and source of the p-channel transistor are located in an n-doped substrate. The n-doped source and drain of the n-channel transistor are placed in a p-doped well for isolation purpose. This well is again located in the substrate. This arrangement acts as a thyristor where the anode and the cathode are connected to the supply terminals of the circuits, while all inputs and outputs are the gates of the thyristor. By driving a sufficient current into any input or output the thyristor will be fired causing a short circuit between the supply terminals (latch-up). This overload will immediately destroy the integrated circuit.

To avoid latch-up semiconductor manufacturers place guards rings inside the integrated circuits. These p- or n-doped areas connected to the positive and negative supply rails respectively surround the critical parts of the circuits. They provide additional collectors for the parasitic transistors which short most of the current which may fire the thyristor to the supply rails. This technique reduces the sensitivity of the thyristor in such way that under normal operation latch-up will be avoided.

European Mixed Signal &amp; Logic Products

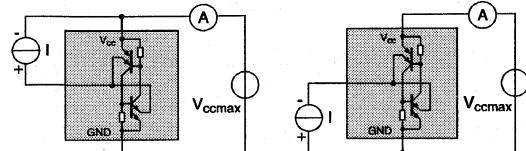

## Latch-up Test Circuit

Family  $I_{min} @ 125^\circ C$

SN74HC 300mA

SN74AC 500mA

SN74BCT 500mA

SN74ABT 500mA

EH9549/08/009/09/E

## Latch up Test (08010)

During the characterisation process of an integrated circuit a latch-up test is also performed, to check the efficiency of the protection circuits. For this purpose a high positive and negative current is driven into any input or output terminal of the integrated circuit to check if there is any way to fire the thyristor and to cause latch-up. The current pulse in this test has to have a certain length (several microseconds) since the transit frequency of the parasitic transistors is very low ( $f_t \approx 1 \text{ MHz}$ ). A very short pulse is thus hardly able to generate latch-up. Note, that this test is a destructive test. The test is performed at  $T_a = 125^\circ C$  since the current gain of the parasitic transistors, and thus the sensitivity the thyristor increases with temperature. As the table above shows, currents of the order of several 100 milliamperes will not cause latch-up. Therefore in practice state-of-the-art integrated CMOS circuits are immune against latch-up.

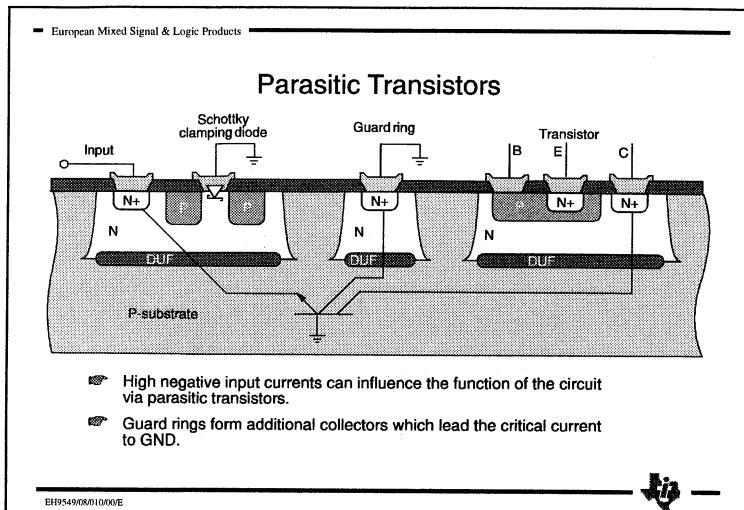

### Parasitic transistors (08010)

The picture above shows the structure of a typical bipolar integrated circuit. On the left side is found the Schottky clamping diode (n-metal junction). This diode limits negative undershoots caused by line reflections. With low negative input currents at this diode the forward voltage of this diode is about 0.5 V. With increasing current the forward voltage of the diode also increases. At a certain current amplitude the forward voltage of the diode becomes higher than 700 mV. At this point the n-p junction to the substrate also starts to conduct. This n-p junction is the base emitter diode of a parasitic transistor, while all n-doped areas in the neighbourhood are the collectors of the parasitic transistors. With a sufficiently high current into the clamping diode and the substrate the parasitic transistor will be turned on. By this the collector of the transistor in the right side in the picture above is pulled to a low level. Due to this undesired effect, the integrated circuit may not function correctly, again.

To avoid these parasitic effects, guard rings are again placed around the input circuitry - in this case the clamping diode. These guard rings perform as an additional collector of the parasitic transistor which shorts most of the current in the substrate to ground. This technique again does not eliminate the parasitic transistor, but it reduces its current gain so far, that under normal operating conditions no malfunction of the integrated circuit will occur. For example, the guard rings of logic circuit of the series SN74xx are designed so that a negative input current  $I_{il} = -60$  mA for a duration  $t_d = 100$  ns will not cause a malfunction of the integrated circuit.

— European Mixed Signal & Logic Products —

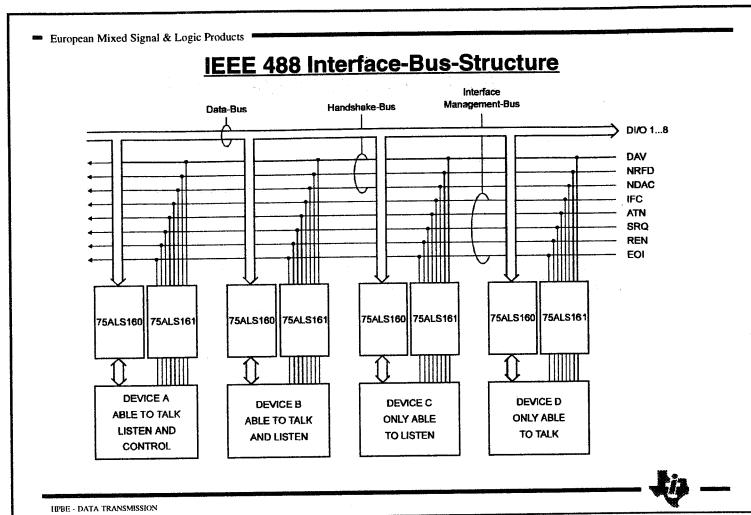

### **IEEE 488 - General Purpose Interface Bus (GPIB)**

- ◆ The IEEE 488 specification describes an universal interface bus, which consists of 8 parallel control lines and 8 parallel data lines.

- ◆ This interface is used for communication between a processor and programmable measurement and similar equipment.

- ◆ The 8 bit parallel data bus works with a data rate of max. 1.5 MByte/s

— GPIB - DATA TRANSMISSION

### IEEE 488 Interface-Bus-Structure

The figure illustrates a typical application of a complex GPIB system. The figure shows the 8 bit data-bus and the 8 bit control bus. Texas Instruments offers in the SN75ALS16x family several transceivers, that meet the IEEE 488 standard.

Careful attention must be paid to the 8 signal lines DAV, NRFD, NDAC, IFC, ATN, REN, and SRQ. Each of the signal line must be twisted with one of the logic ground wires to minimize crosstalk.

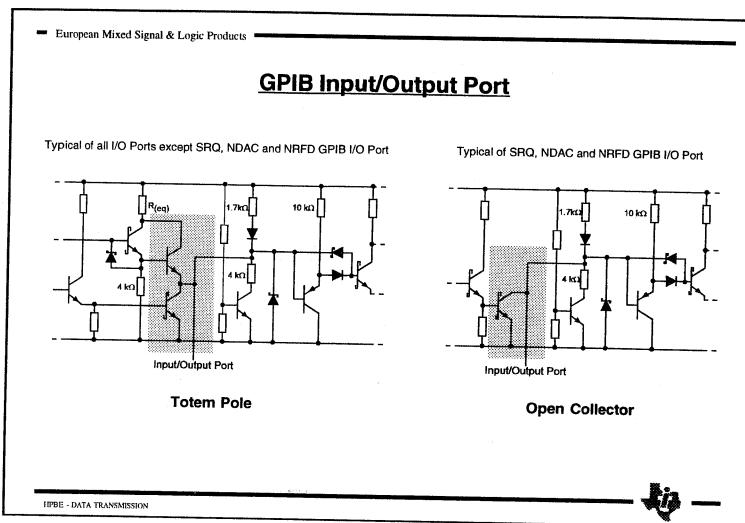

### GPIB Input/Output Port

The typical input/output stages are illustrated in this figure. Outputs are either totem pole or open collector. A totem pole output is required for faster data rates. Open collector outputs must be used, if parallel polling is required (wired-and, wired-or function with multiple lines). The output stages SRQ, NDAC and NRFD are configured as open-collector output stages. All driver outputs feature active bus-terminating resistor circuits, designed to provide high impedance to the bus when  $V_{cc} = 0V$ . The input stages are similar. Each of the inputs consists of a clamping diode to limit the negative undershoots at the end of the line. A further termination is therefore not required.

■ European Mixed Signal & Logic Products

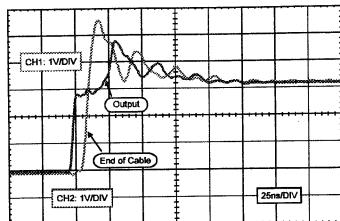

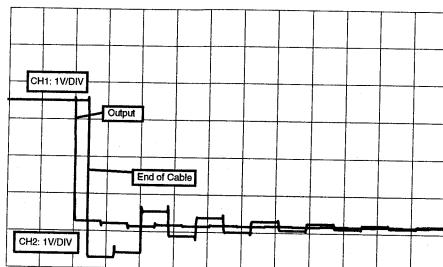

## Measurement of Low-High Transition

### Totem Pole/Open Collector

## **Totem Pole**

## **Open Collector**

## Measurement of Low-High Transition Totem Pole/Open Collector

The figures show the low-high transition of the totem pole and open collector output stage. It is obvious that due to the misterminated line the low-high transition of the open collector output stage is substantial slower than the low-high transition of the totem pole output. The energy to charge the capacitance of the line has to be provided via the high impedance resistor network in the bus interface circuits.

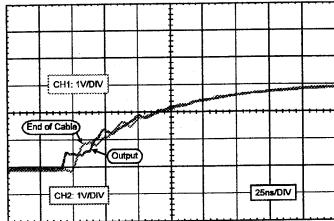

**Simulation of Low-High Transition Totem Pole/ Open Collector**

The simulation of both output stages show the same result as the measurement.

— European Mixed Signal & Logic Products —

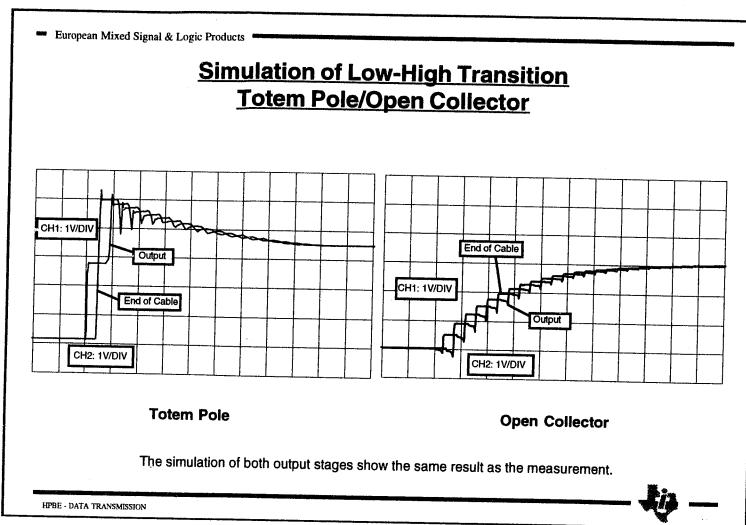

### Measurement of High-Low Transition

The high-low transition is similar for the totem pole and open collector output stage. The negative undershoots at the end of the line are limited through the internal clamping diode.

— TIP0410A00700R - DATA TRANSMISSION —

### **Measurement of High-Low Transition**

The high-low transition is similar for the totem pole and open collector output stage, because the output impedance in the low case of the open collector- and of the totem pole output stage are the same. The negative undershoots at the end of the line are limited through the internal clamping diode. A further clamping diode is therefore not required.

— European Mixed Signal & Logic Products —

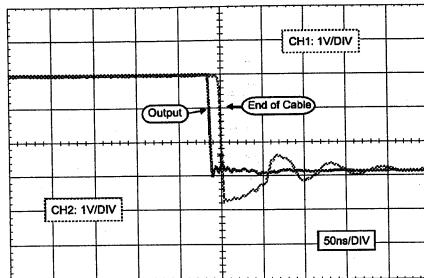

**Simulation of High-Low Transition**

The simulation of the high-low transition confirms the measurement.

— HBEE - DATA TRANSMISSION —

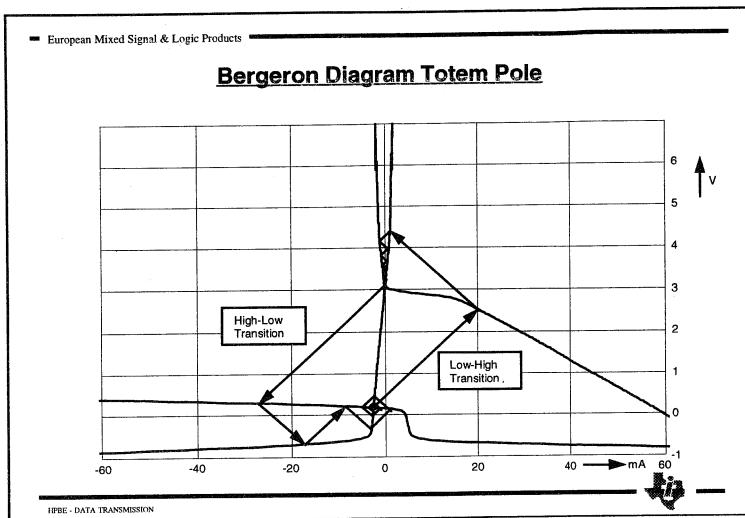

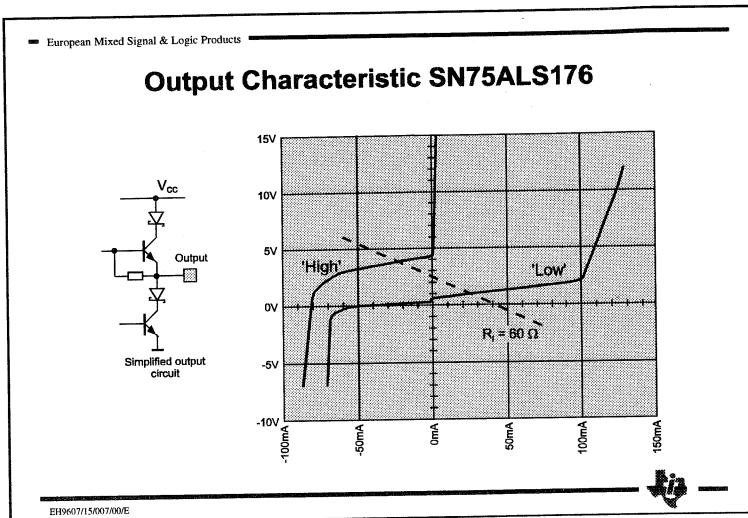

### Bergeron Diagram Totem Pole

As already mentioned in the section 'Basics and Practical Examples of Transmission', the Bergeron Diagram is a simple tool to analyse line reflections in circuits which show nonlinear characteristics as in semiconductor components. The picture above shows the Bergeron Diagram for the totem-pole output stage with its voltage/current diagram, the output characteristic of the driver for the low and high case, and the input characteristic of the receiver. The drawing lines with the alternating slopes show the voltages at the end and at the beginning of the line. The Bergeron Diagram confirms the results of the measurement and simulation.

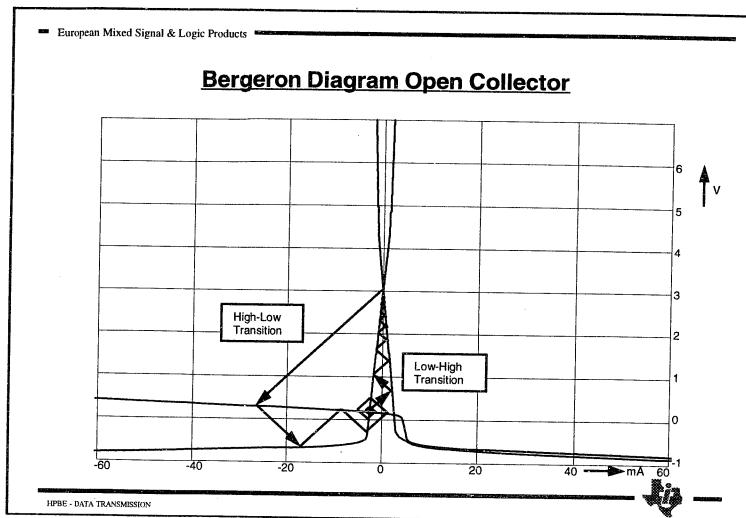

### Bergeron Diagram Open Collector

The Bergeron Diagram confirms that the low-high transition of the open collector output stage is very slow.

— European Mixed Signal & Logic Products —

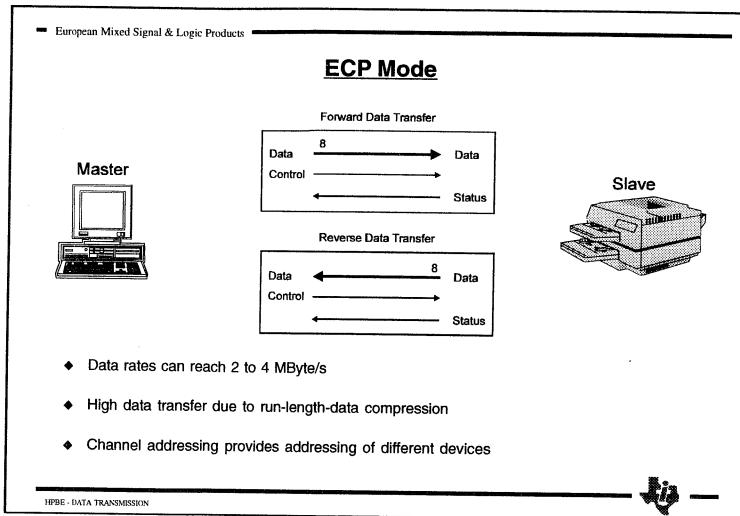

**IEEE 1284**

- ◆ Adds bi-directional capabilities to the existing "Centronics Parallel Interface"

- ◆ Multiple bi-directional operating modes

- ◆ Advanced operating mode can reach speeds of 2 to 4 Mbyte/s

- ◆ New electrical interface, cabling and connector for improved performance and reliability while retaining backward compatibility.

— IEEE - DATA TRANSMISSION —

**IEEE 1284**

The IEEE 1284 standard, "Standard Signaling Method for a Bi-directional Parallel Peripheral Interface for Personal Computers" was created because there existed no defined standard for bidirectional parallel communications between personal computers and peripherals. Pre-existing methods used a wide variety of hardware and software products, each with unique and incompatible signaling schemes. This standard was developed to provide an open path for communications between computers and more intelligent printers and peripherals.

— European Mixed Signal & Logic Products —

### **IEEE 1284 Overview**

#### **5 operating modes:**

- ◆ Compatible

- ◆ Nibble

- ◆ Byte

- ◆ ECP - Enhanced Capabilities Port

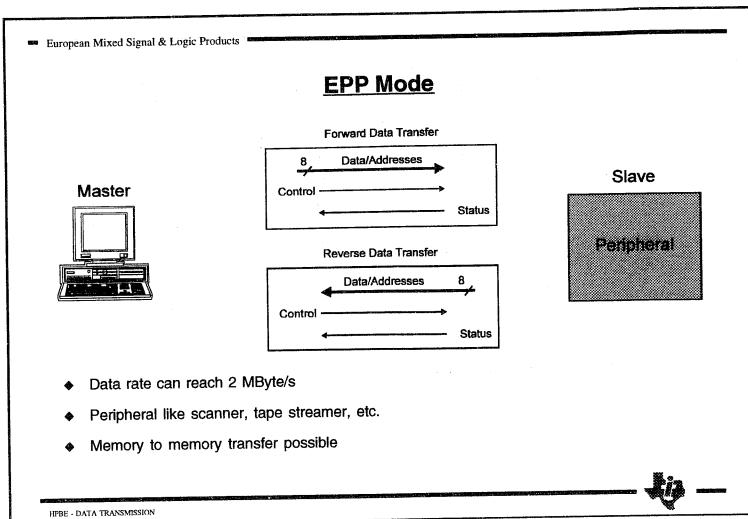

- ◆ EPP - Enhanced Parallel Port

— HP84 - DATA TRANSMISSION —

### **IEEE 1284 Overview**

The interface supports a number of distinct communication modes. The following figures give a brief description of the different modes.

### Nibble/Byte Mode

The Compatibility Mode provides host to peripheral communications in a manner compatible with the traditional uni-directional interface.

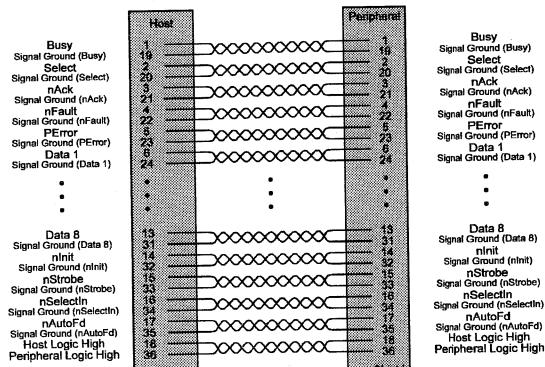

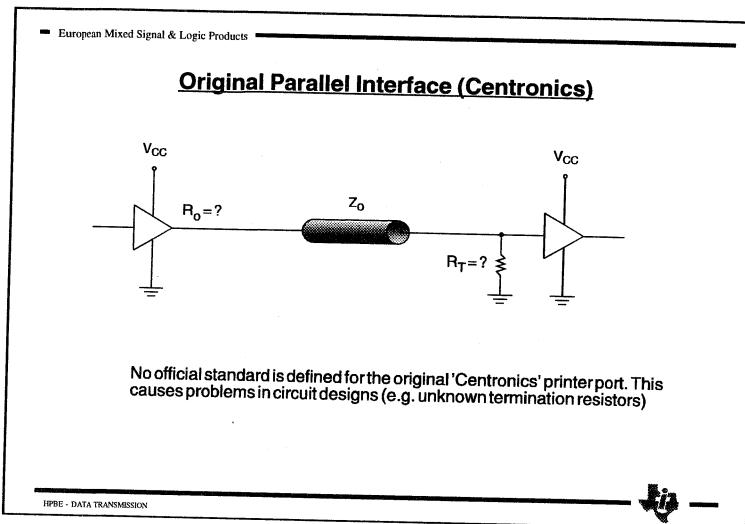

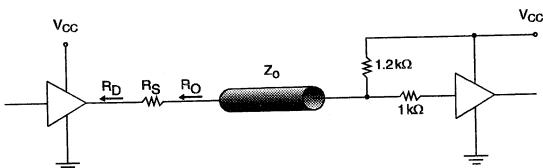

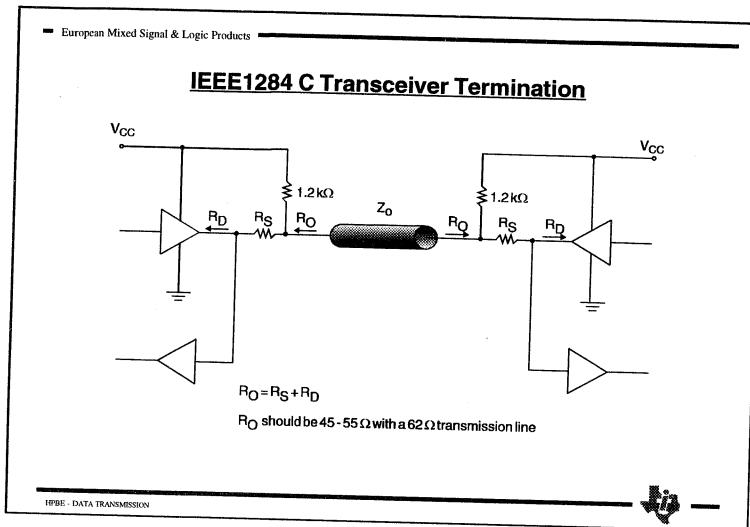

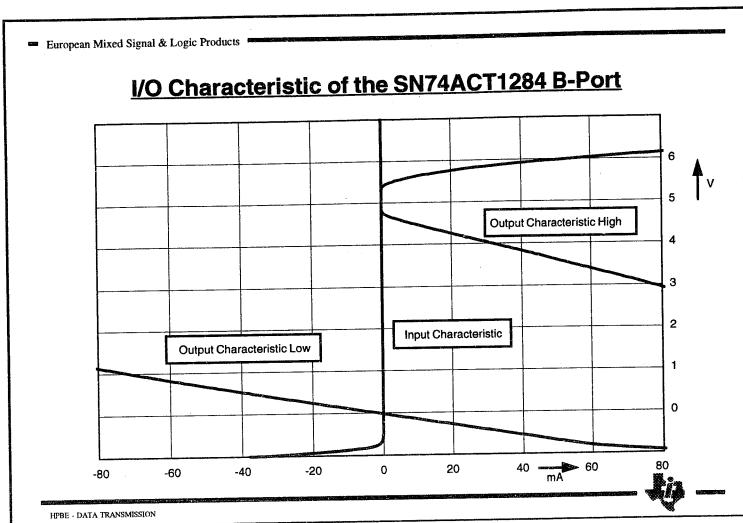

In the Nibble and Byte Modes of operation, data from the host to printer is sent using the compatibility mode of operation. Data is sent over the 8 data lines in parallel. The reverse data transfer, peripheral to host, can be achieved in one of two ways.; either 4 bits, a nibble at a time, or 8 bits, a byte at a time. In the Nibble Mode, transfer of data from the printer to the host is accomplished using 4 of the printer status lines. The advantage of the nibble mode is that data transfer can be functionally implemented totally in a software driver on the installed base of personal computers.